Эффективный объединенный блок умножения/накопления с использованием мультиоперандного параллельного префиксного сумматора

DOI:

https://doi.org/10.20535/S0021347022040057Ключові слова:

мультиоперандный сумматор, объединенный блок умножения/накопления, параллельный префиксный сумматор, арифметическое устройствоАнотація

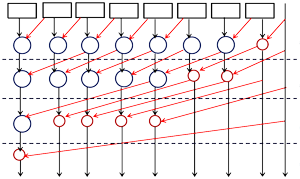

В статье разработаны и реализованы различные мультиоперандные параллельные префиксные сумматоры в объединенном блоке умножения/накопления MAC (multiply-accumulate). Мультиоперандное суммирование — улучшенный метод по сравнению с методом с использованием набора 2-операндных сумматоров во многих арифметических приложениях. Также, параллельный префиксный сумматор является одним из наиболее быстродействующих сумматоров. Таким образом, мультиоперандные сумматоры разрабатываются с использованием различных параллельных префиксных графов, которые используются для реализации объединенного MAC блока. Вначале в работе рассмотрены и проанализированы параллельные префиксные сумматоры. Далее структура данных разработанных сумматоров изменена для выполнения мультиоперандных операций, и разработан MAC блок с использованием различных мультиоперандных сумматоров на базе Xilinx Kintex 7 FPGA. Мультиоперандный сумматор Ладнера–Фишера обеспечивает оптимальные результаты относительно энергопотребления, площади и задержки, по сравнению с существующими аналогами. В соответствии с результатами, полученными в Kintex 7 FPGA, он имеет сниженное на 38,06% энергопотребление, на 17,54% — задержку распространения, и на 26,55% — количество LUT, по сравнению с существующим мультиоперандным сумматором. Соответственно, объединенный MAC блок на основе такого сумматора Ладнера–Фишера обеспечивает снижение энергопотребления на 39,95%, задержку распространения на 16,83%, и количество LUT — на 13,73%, по сравнению с классическим МАС блоком.

Посилання

- S. Singh, R. Waxman, “Multiple operand addition and multiplication,” IEEE Trans. Comput., vol. C–22, no. 2, pp. 113–120, 1973, doi: https://doi.org/10.1109/T-C.1973.223670.

- L. Tu, Y. Yuan, K. Huang, X. Zhang, D. Chen, Z. Wang, “Improved synthesis of compressor trees in high-level synthesis for modern FPGAs,” IEEE Trans. Comput. Des. Integr. Circuits Syst., vol. 37, no. 12, pp. 3206–3210, 2018, doi: https://doi.org/10.1109/TCAD.2018.2801241.

- K. R. Gavali, N. Choudhary, S. Mishra, S. Dubey, “A parallel pipelined adder suitable for FPGA implementation,” in 2018 International Conference on Smart City and Emerging Technology (ICSCET), 2018, pp. 1–4, doi: https://doi.org/10.1109/ICSCET.2018.8537358.

- S. Kannappan, S. Aruna Mastani, “A novel multi-operand adder design using multiplexers,” in 2017 IEEE International Conference on Computational Intelligence and Computing Research (ICCIC), 2017, pp. 1–4, doi: https://doi.org/10.1109/ICCIC.2017.8524157.

- R. D. Kenney, M. J. Schulte, “High-speed multioperand decimal adders,” IEEE Trans. Comput., vol. 54, no. 8, pp. 953–963, 2005, doi: https://doi.org/10.1109/TC.2005.129.

- J. Villalba, J. Hormigo, J. M. Prades, E. L. Zapata, “On-line multioperand addition based on on-line full adders,” in 2005 IEEE International Conference on Application-Specific Systems, Architecture Processors (ASAP’05), 2005, pp. 322–327, doi: https://doi.org/10.1109/ASAP.2005.50.

- Д. В. Морозов, М. М. Пилипко, “Схемотехническое решение одноразрядного двоичного КМОП сумматора,” Микроэлектроника, Т. 42, № 2, с. 146–152, 2013, doi: https://doi.org/10.7868/S0544126913020099.

- М. М. Пилипко, Д. В. Морозов, “Сравнительный анализ схем КМОП сумматоров на 10 транзисторах,” Известия вузов. Радиоэлектроника, Т. 57, № 9, с. 42–54, 2014, doi: https://doi.org/10.20535/S0021347014090040.

- J. Hormigo, J. Villalba, E. L. Zapata, “Multioperand redundant adders on FPGAs,” IEEE Trans. Comput., vol. 62, no. 10, pp. 2013–2025, 2013, doi: https://doi.org/10.1109/TC.2012.168.

- S. D. Thabah, M. Sonowal, P. Saha, “Experimental studies on multi-operand adders,” Int. J. Smart Sens. Intell. Syst., vol. 10, no. 2, pp. 1–14, 2017, doi: https://doi.org/10.21307/ijssis-2017-214.

- B. Khurshid, R. N. Mir, “High efficiency generalized parallel counters for Xilinx FPGAs,” in 2015 IEEE 22nd International Conference on High Performance Computing (HiPC), 2015, pp. 40–46, doi: https://doi.org/10.1109/HiPC.2015.41.

- M. Kumm, J. Kappauf, “Advanced compressor tree synthesis for FPGAs,” IEEE Trans. Comput., vol. 67, no. 8, pp. 1078–1091, 2018, doi: https://doi.org/10.1109/TC.2018.2795611.

- S. Akash, M. Ajeeth, N. Radha, “An efficient implementation of FIR filter using high speed adders for signal processing applications,” in 2020 Second International Conference on Inventive Research in Computing Applications (ICIRCA), 2020, pp. 1047–1051, doi: https://doi.org/10.1109/ICIRCA48905.2020.9183114.

- A. Abinaya, M. Maheswari, A. S. Alqahtani, “Heuristic analysis of CIC filter design for next-generation wireless applications,” Arab. J. Sci. Eng., vol. 46, no. 2, pp. 1257–1268, 2021, doi: https://doi.org/10.1007/s13369-020-05016-1.

- V. Pudi, K. Sridharan, “Low complexity design of ripple carry and Brent–Kung adders in QCA,” IEEE Trans. Nanotechnol., vol. 11, no. 1, pp. 105–119, 2012, doi: https://doi.org/10.1109/TNANO.2011.2158006.

- N. Varshney, G. Arya, “Design and execution of enhanced carry increment adder using Han-Carlson and Kogge-Stone adder technique : Han-Carlson and Kogge-Stone adder is used to increase speed of adder circuitry,” in 2019 3rd International conference on Electronics, Communication and Aerospace Technology (ICECA), 2019, pp. 1163–1170, doi: https://doi.org/10.1109/ICECA.2019.8822194.

- A. K. Panda, R. Palisetty, K. C. Ray, “High-speed area-efficient VLSI architecture of three-operand binary adder,” IEEE Trans. Circuits Syst. I Regul. Pap., vol. 67, no. 11, pp. 3944–3953, 2020, doi: https://doi.org/10.1109/TCSI.2020.3016275.

- N. Nasiri, O. Segal, M. Margala, “Modified fused multiply-accumulate chained unit,” in 2014 IEEE 57th International Midwest Symposium on Circuits and Systems (MWSCAS), 2014, pp. 889–892, doi: https://doi.org/10.1109/MWSCAS.2014.6908558.

- H. Zhang, H. J. Lee, S.-B. Ko, “Efficient fixed/floating-point merged mixed-precision multiply-accumulate unit for deep learning processors,” in 2018 IEEE International Symposium on Circuits and Systems (ISCAS), 2018, pp. 1–5, doi: https://doi.org/10.1109/ISCAS.2018.8351354.

- D. Esposito, D. De Caro, A. G. M. Strollo, “Variable latency speculative parallel prefix adders for unsigned and signed operands,” IEEE Trans. Circuits Syst. I Regul. Pap., vol. 63, no. 8, pp. 1200–1209, 2016, doi: https://doi.org/10.1109/TCSI.2016.2564699.