Нейронный входной подпороговый КМОП-усилитель сверхмалой мощности с высоким входным импедансом

DOI:

https://doi.org/10.20535/S0021347019030051Ключові слова:

входной усилитель, подпороговый, двойная МОП структура, ток утечки, входной импедансАнотація

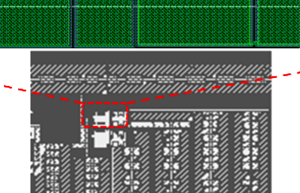

В статье предложен входной усилитель (ВУ) сверхмалой мощности с управлением по напряжению, который предназначен для нейронных применений и отличается подпороговой (subthreshold) конструкцией. За последние несколько десятилетий этой теме посвящено много исследовательских работ в области вживляемых медицинских протезов, ориентированных на контроль и лечение неврологических расстройств, таких как слуховые дисфункции и нарушения функции зрения, эпилепсия, болезнь Паркинсона, паралич. ВУ выполняет важную функцию по обнаружению сигнала в системах неврологического мониторинга для обеспечения точности воспроизведения биосигналов. Согласованная схема на базе двойной МОП структуры с обратной связью используется для компенсации входных токов утечки, генерируемых малошумящим усилителем, выполненным в виде интегральной схемы, что является главной причиной очень большой потери сигнала в цепи смещения на входе. Эта топология с замкнутым контуром обеспечивает поддержание высокого импеданса ВУ в широком диапазоне частот входного сигнала. Предлагаемый ВУ выполнен при использовании 0,18 мкм КМОП-технологии компании SK Hynix. Этот ВУ потребляет мощность 320 нВт при занимаемой площади 0,016 мм2 и достигает значения входного импеданса 44,9 ГОм при уровне шума 153 нВ/Гц1/2, приведенного ко входу.Посилання

- Rajabpour-Moghaddam, K.; Mohammadi, A. “A wireless multi-channel implantable neural recording microsystem based on optimized analog TDM-FDM combination,” AEU - Int. J. Electron. Commun., Vol. 77, p. 130-138, 2017. DOI: https://doi.org/10.1016/j.aeue.2017.04.011.

- Sung, Y.-S.; Chen, W.-M.; Wu, C.-Y. “The design of 8-channel CMOS area-efficient low-power current-mode analog front-end amplifier for EEG signal recording,” Proc. of IEEE Int. Symp. on Circuits and Systems, 22-25 May 2016, Montreal, Canada. IEEE, 2016, p. 530-533. DOI: https://doi.org/10.1109/ISCAS.2016.7527294.

- Zhou, Z.; Warr, P. A. “Back-gate current neutralisation feedback loop for high-input impedance neural FEAs,” Electron. Lett., Vol. 52, No. 19, p. 1586-1588, 2016. DOI: https://doi.org/10.1049/el.2016.2178.

- Zhang, F.; Holleman, J.; Otis, B. P. “Design of ultra-low power biopotential amplifiers for biosignal acquisition applications,” IEEE Trans. Biomed. Circuits Syst., Vol. 6, No. 4, p. 344-355, 2012. DOI: https://doi.org/10.1109/TBCAS.2011.2177089.

- Barsakcioglu, D. Y.; Liu, Yan; Bhunjun, P.; Navajas, J.; Eftekhar, A.; Jackson, A.; Quiroga, R. Q.; Constandinou, T. G. “An analogue front-end model for developing neural spike sorting systems,” IEEE Trans. Biomed. Circuits Syst., Vol. 8, No. 2, p. 216-227, 2014. DOI: https://doi.org/10.1109/TBCAS.2014.2313087.

- Борисов, С. А.; Коротков, А. С. “Методика построения высокочастотной малосигнальной модели МОП-транзистора,” Известия вузов. Радиоэлектроника, Т. 53, № 7, С. 21–30, 2010. URI: http://radio.kpi.ua/article/view/S0021347010070034.

- Demosthenous, A.; Pachnis, I.; Jiang, D.; Donaldson, N. “An integrated amplifier with passive neutralization of myoelectric interference from neural recording tripoles,” IEEE Sens. J., Vol. 13, No. 9, p. 3236-3248, 2013. DOI: https://doi.org/10.1109/JSEN.2013.2271477.

- Mohseni, P.; Najafi, K. “A fully integrated neural recording amplifier with DC input stabilization,” IEEE Trans. Biomed. Eng., Vol. 51, No. 5, p. 832-837, 2004. DOI: https://doi.org/10.1109/TBME.2004.824126.

- Harrison, R. R.; Charles, C. “A low-power low-noise CMOS amplifier for neural recording applications,” IEEE J. Solid-State Circuits, Vol. 38, No. 6, p. 958-965, 2003. DOI: https://doi.org/10.1109/JSSC.2003.811979.

- Ferrari, G.; Farina, M.; Guagliardo, F.; Carminati, M.; Sampietro, M. “Ultra-low-noise CMOS current preamplifier from DC to 1 MHz,” Electron. Lett., Vol. 45, No. 25, p. 1278-1280, 2009. DOI: https://doi.org/10.1049/el.2009.2353.

- Magnelli, L.; Amoroso, F. A.; Crupi, F.; Cappuccino, G.; Iannaccone, G. “Design of a 75-nW, 0.5-V subthreshold complementary metal-oxide-semiconductor operational amplifier,” Int. J. Circuit Theory Appl., Vol. 42, No. 9, p. 967-977, 2014. DOI: https://doi.org/10.1002/cta.1898.

- Nevalainen, T.; Koivisto, T.; Pankaala, M. “Subthreshold nano-watt front-end amplifier for wireless ECG applications,” Proc. of 32nd NORCHIP Conf. Nord Microelectron. Event, 27-28 Oct. 2014, Tampere, Finland. IEEE, 2015, p. 1-4. DOI: https://doi.org/10.1109/NORCHIP.2014.7004713.

- Zhou, Z.; Warr, P. A. “A high input impedance low noise integrated front-end amplifier for neural monitoring,” IEEE Trans. Biomed. Circuits Syst., Vol. 10, No. 6, p. 1-8, 2016. DOI: https://doi.org/10.1109/TBCAS.2016.2525810.

- Wu, C.-Y.; Chen, W.-M.; Kuo, L.-T. “A CMOS power-efficient low-noise current-mode front-end amplifier for neural signal recording,” IEEE Trans. Biomed. Circuits Syst., Vol. 7, No. 2, p. 107-114, 2013. DOI: https://doi.org/10.1109/TBCAS.2013.2256422.

- Shulyzki, R.; Abdelhalim, K.; Bagheri, A.; Salam, M. T.; Florez, C. M.; Velazquez, J. L. P.; Carlen, P. L.; Genov, R. “320-channel active probe for high-resolution neuromonitoring and responsive neurostimulation,” IEEE Trans. Biomed. Circuits Syst., Vol. 9, No. 1, p. 34-49, 2015. DOI: https://doi.org/10.1109/TBCAS.2014.2312552.

- Abdi, A.; Cha, H.-K. “A bidirectional neural interface CMOS analog front-end IC with embedded isolation switch for implantable devices,” Microelectronics J., Vol. 58, p. 70-75, 2016. DOI: https://doi.org/10.1016/j.mejo.2016.10.013.

##submission.downloads##

Опубліковано

2019-03-30

Як цитувати

Хан, С. Р., & Надим, И. (2019). Нейронный входной подпороговый КМОП-усилитель сверхмалой мощности с высоким входным импедансом. Вісті вищих учбових закладів. Радіоелектроніка, 62(3), 167–176. https://doi.org/10.20535/S0021347019030051

Номер

Розділ

Оригінальні статті