Высокоэффективная схема генератора подкачки заряда с перекрестными связями и четырьмя тактовыми сигналами

DOI:

https://doi.org/10.20535/S002134701812004XКлючові слова:

генератор подкачки заряда с перекрестными связями, обратные потери мощности, напряжение пульсаций, четырехтактная схемаАнотація

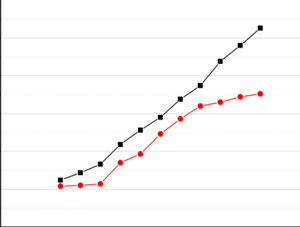

Предложена монолитная схема генератора подкачки заряда с перекрестными обратными связями и четырьмя тактовыми сигналами для преобразователя постоянного напряжения в постоянное напряжение (DC-DC). При использовании указанной новой схемы тактовых сигналов такой преобразователь не имеет обратных потерь мощности и обладает уменьшенным напряжением пульсаций. Кроме того, максимальная разница напряжений между выводами всех транзисторов не превышает уровня напряжения питания, что позволяет решить проблему перенапряжения подзатворного оксида в традиционных схемах генератора подкачки заряда и повысить надежность. Предлагаемая схема генератора подкачки заряда не требует дополнительной схемы сдвига уровня, в результате чего коэффициент полезного действия увеличивается. Проведено моделирование предлагаемой схемы генератора подкачки заряда при использовании Spectre для моделирования 0,18 мкм КМОП-технологии фирмы TSMC. Результаты моделирования показали, что максимальный кпд преобразования напряжения для новой трехкаскадной схемы с перекрестными связями при входном напряжении 1,5 В составляет 99,8%. Результаты сравнения традиционного и предлагаемого усовершенствованного генератора подкачки заряда дают существенное уменьшение пульсаций напряжения на выходе последнего.Посилання

- Dickson, J. F. “On-chip high-voltage generation in MNOS integrated circuits using an improved voltage multiplier technique,” IEEE J. Solid-State Circuits, Vol. 11, No. 3, p. 374-378, 1976. DOI: https://doi.org/10.1109/JSSC.1976.1050739.

- Wu, J. T.; and Chang, K.-L. “MOS charge pumps for low-voltage operation,” IEEE J. Solid-State Circuits, Vol. 33, No. 4, p. 592-597, 1998. DOI: https://doi.org/10.1109/4.663564.

- Ker, M.-D.; Chen, S.-L.; and Tsai, C. S. “Design of charge pump circuit with consideration of gate-oxide reliability in low-voltage CMOS processes,” IEEE J. Solid-State Circuits, Vol. 41, No. 5, p. 1100-1107, 2006. DOI: https://doi.org/10.1109/JSSC.2006.872704.

- Lee, H.; and Mok, P. K. T. “Switching noise and shoot-through current reduction techniques for switched-capacitor voltage doubler,” IEEE J. Solid-State Circuits, Vol. 40, No. 5, p. 1136-1146, 2005. DOI: https://doi.org/10.1109/JSSC.2005.845978.

- Das, T.; Prasad, S.; Dam, S.; and Mandal, P. “A pseudo cross-coupled switch-capacitor based DC-DC boost converter for high efficiency and high power density,” IEEE Trans. Power Electronics, Vol. 29, No. 11, p. 5961-5974, 2014. DOI: https://doi.org/10.1109/TPEL.2014.2297972.

- Kim, J.-Y.; Park, S.-J.; Kwon, K.-W.; Kong, B.-S.; Choi, J.-S.; and Jun, Y.-H. “CMOS charge pump with no reversion loss and enhanced drivability,” IEEE Trans. Very Large Scale Integration Systems, Vol. 22, No. 6, p. 1441-1445, 2014. DOI: https://doi.org/10.1109/TVLSI.2013.2267214.

- Mui, T. W.; Ho, M.; Mak, K. H.; Guo, J.; Chen, H.; and Leung, K. N. “An area-efficient 96.5%-peak-efficiency cross-coupled voltage doubler with minimum supply of 0.8 V,” IEEE Trans. Circuits Systems II: Express Briefs, Vol. 61, No. 9, p. 656-660, 2014. DOI: https://doi.org/10.1109/TCSII.2014.2331109.

##submission.downloads##

Опубліковано

2018-12-27

Як цитувати

Ма, М., Цай, С., Цзян, Ц., & Сун, И. (2018). Высокоэффективная схема генератора подкачки заряда с перекрестными связями и четырьмя тактовыми сигналами. Вісті вищих учбових закладів. Радіоелектроніка, 61(12), 710–717. https://doi.org/10.20535/S002134701812004X

Номер

Розділ

Оригінальні статті