Усовершенствованная ячейка SRAM с большим статическим запасом помехоустойчивости и повышенной стабильностью c применением мемристоров 45-нм технологии

DOI:

https://doi.org/10.20535/S0021347018050035Ключові слова:

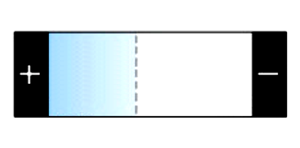

напряжение шума, RSNM, WSNM, коэффициент ячейки, коэффициент нагрузки, мемристор, ячейка 7T SRAMАнотація

Технология сверхбольших интегральных схем VLSI (very large scale integrated) завоевала популярность благодаря возможности значительного изменения и адаптации. Развитие данных платформ идет по пути уменьшения размеров элементов. Но происходит не только уменьшение размеров, но и революция в конструировании, когда все схемы переключаются с уровня единичных элементов к уровню других появляющихся устройств. В этой борьбе мемристоры более способны закрепится в области VLSI по сравнению с другими новыми устройствами. В данной работе представлено изучение статического запаса помехоустойчивости, подчеркивается новая проблема точности, поскольку шум оказывает большое влияние на напряжение удержания ячейки SRAM и это влияние в мемристорной ячейке меньше, чем для традиционной ячейки 7T SRAM. Результаты имитационного моделирования представлены для ячейки 7T SRAM и мемристорной 7T SRAM ячейки технологии 45 нм. В данной работе обсуждается и сравнивается влияние коэффициентов ячейки и нагрузки.Посилання

- Bowman, K. A.; Duvall, S. G.; Meindl, J. D. “Impact of die-to-die and within-die parameter fluctuations on the maximum clock frequency distribution for gigascale integration,” IEEE J. Solid-State Circuits, Vol. 37, No. 2, P. 183-190, Feb. 2002. DOI: https://doi.org/10.1109/4.982424.

- Borkar, S.; Karnik, T.; Narendra, S.; Tschanz, J.; Keshavarzi, A.; De, V. “Parameter variations and impact on circuits and microarchitecture,” Proc. of 40th Annual Design Automation Conf., 2-6 Jun. 2003, Anaheim, CA, USA. ACM, 2006, pp. 338-342. DOI: https://doi.org/10.1145/775832.775920.

- Karnik, T.; De, V.; Borkar, S. “Statistical design for variation tolerance: key to continued Moore’s law,” Proc. of Int. Conf. on Integrated Circuit Design and Technology, 17-20 May 2004, Austin, TX, USA. IEEE, 2004, pp. 175-176. DOI: https://doi.org/10.1109/ICICDT.2004.1309939.

- Doyle, S.; Ramaswamy, S.; Hoang, T.; Rockett, L.; Grembowski, T.; Bumgarner, A. “High performance radiation hardened static random access memory (SRAM) design for space applications,” Proc. of IEEE Aerospace Conf., 6-13 Mar. 2004, Big Sky, MT, USA. IEEE, 2004, pp. 2284-2293. DOI: https://doi.org/10.1109/AERO.2004.1368022.

- Chua, L. “Memristor-The missing circuit element,“ IEEE Trans. Circuit Syst., Vol. 18, No. 5, P. 507-519, 1971. DOI: https://doi.org/10.1109/TCT.1971.1083337.

- Strukov, D. B.; Snider, G. S.; Stewart, D. R.; Williams, R. Stanley. “The missing memristor found,” Nature, Vol. 453, P. 80-83, 2008. DOI: https://doi.org/10.1038/nature06932.

- Itoh, M.; Chua, L. O. “Memristor oscillators,” Int. J. Bifurcation Chaos, Vol. 18, No. 11, P. 3183-3206, 2008. DOI: https://doi.org/10.1142/S0218127408022354.

- Mukherjee, Debasis; Mondal, Hemanta Kr.; Reddy, B. V. R. “Static noise margin analysis of SRAM cell for high speed application,” Int. J. Computer Science Issues, Vol. 7, No. 5, Sept. 2010. URI: https://www.ijcsi.org/papers/7-5-175-180.pdf.

- Chandrakasan, A. P.; Sheng, S.; Brodersen, R. W. “Low-power CMOS digital design,” IEEE J. Solid-State Circuits, Vol. 27, No. 4, P. 473-484, Apr. 1992. DOI: https://doi.org/10.1109/4.126534.

- Pavlov, Andrei; Sachdev, Manoj. CMOS SRAM Circuit Design and Parametric Test in Nano-Scaled Technologies. Springer, 2008. DOI: http://doi.org/10.1007/978-1-4020-8363-1.

- Kang, Sung-Mo; Leblebici, Yusuf. CMOS Digital Integrated Circuits: Analysis & Design, 3rd ed. McGraw-Hill Education, 2002.

- Singh, Shalini; Sable, Varun; Baghel, Vijay Singh; Akashe, Shyam. “Memory device with non-volatile memory array including one FinFET one memristor (1F1M),” Ref. No. 3093/MUM/2015, Pub. 11 Sept. 2015, India.

- Rabaey, Jan M.; Chandrakasan, Anantha; Nikolic, Borivoje. Digital Integrated Circuits, 2nd ed. Pearson, 2003.

##submission.downloads##

Опубліковано

2018-05-27

Як цитувати

Сингх, Ш., & Мишра, В. (2018). Усовершенствованная ячейка SRAM с большим статическим запасом помехоустойчивости и повышенной стабильностью c применением мемристоров 45-нм технологии. Вісті вищих учбових закладів. Радіоелектроніка, 61(5), 267–274. https://doi.org/10.20535/S0021347018050035

Номер

Розділ

Оригінальні статті