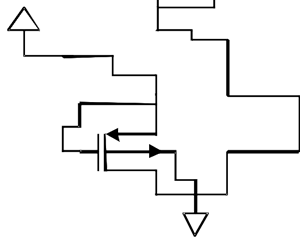

Анализ влияния расширенной конфигурации n-МОП транзистора на параметры 4x1 мультиплексора

DOI:

https://doi.org/10.20535/S0021347018030044Ключові слова:

расширенный n-МОП транзистор со статическим порогом, ST-ATNMOS, расширенный p-МОП транзистор с закороченным участком затвор-исток и n-МОП структурой, ASG-S PMOS-NMOS, мощность утечки, задержкаАнотація

В статье приведен анализ потребляемой мощности и величины задержки 4x1 мультиплексора на базе расширенной конфигурации n-МОП транзистора AT-NMOS (Augmented Transistor NMOS). Рассмотрено влияние различных уровней общей ширины канала транзистора на характеристики мощности утечки и задержки в случае 45 нм технологии. Установлено, что параметр эффективности улучшается в предлагаемой конструкции на основе расширенной конфигурации p-МОП транзистора с закороченным участком затвор–исток и n-МОП структурой ASG-S PMOS-NMOS (Augmented Shorted Gate-Source PMOS with NMOS) по сравнению с 4x1 мультиплексором на основе конфигурации расширенного n-МОП транзистора со статическим порогом ST-ATNMOS (Static Threshold AT-NMOS). При этой комбинации получены желаемые параметры рабочей характеристики проектируемой схемы. В работе рассмотрено два типа моделей для 4x1 мультиплексора. Показано, что мощность утечки существенно сокращается. Характеристика задержки также улучшается до 5% при источнике питания 1 В в случае рассмотрения многоуровневой ширины канала транзистора для оценки моделей 4x1 мультиплексора на основе различных конфигураций расширенного n-МОП транзистора AT-NMOS. Моделирование осуществлялось при использовании моделирующих программ Cadence Analog Virtuoso и Spectre Simulator применительно к 45 нм КМОП-технологии.Посилання

- Poon, K. W.; Yan, A.; Wilton, S. J. E. “A flexible power model for FPGAs,” Int. Conf. on Field Programmable Logic and Applications, pp. 312–321, 2002. DOI: http://doi.org/10.1007/3-540-46117-5_33.

- Khouri, K. S.; Jha, N. K. “Leakage power analysis and reduction during behavioral synthesis,” IEEE Trans. Very Large Scale Integration (VLSI) Systems, vol. 10, no. 6, pp. 876–885, 2002. DOI: https://doi.org/10.1109/TVLSI.2002.808436.

- Shang, L.; Kaviani, A. S.; Bathala, K. “Dynamic power consumption in Virtex-II FPGA family,” Proc. of ACM/SIGDA Int. Symp. on Field-Programmable Gate Arrays, 2002, pp. 157–164. DOI: http://doi.org/10.1145/503048.503072.

- Gracia, A. “Power consumption and optimization in field programmable gate arrays,” Ph. D. thesis, Departement Communications et Electronique, Ecole Nationale Superieuredes Telecommunications, 2000.

- Chun, J. W.; Chen, C. Y. R. “A novel leakage power reduction technique for CMOS circuit design,” Proc. of SoC Design Conf., ISOCC, 22–23 Nov. 2010, Seoul, South Korea. IEEE, 2010, pp. 119–122. DOI: https://doi.org/10.1109/SOCDC.2010.5682957.

- Allan, A.; Edenfeld, D.; Joyner, W. H.; Khang, A. B.; Rodgers, M.; Zorian, Y. “2001 technology roadmap for semiconductors,” Computer, Vol. 35, No. 1, pp. 42–53, 2002. DOI: https://doi.org/10.1109/2.976918.

- Sylvester, D.; Kaul, H. “Future performance challenges in nanometer design,” Proc. of Design Automation Conf., 22 Jun. 2001, Las Vegas, NV, USA. IEEE, 2001, pp. 3–8. DOI: https://doi.org/10.1145/378239.378245.

- Halter, J. P.; Najm, F. N. “A gate-level leakage power reduction method for ultra-low power CMOS circuits,” Proc. of Custom Integrated Circuits Conf., 5–8 May 1997, Santa Clara, CA, USA. IEEE, 1997, pp. 475–478. DOI: https://doi.org/10.1109/CICC.1997.606670.

- Taun, T.; Lai, B. “Leakage power analysis of a 90nm FPGA,” Proc. of Custom Integrated Circuits Conf., 24 Sept. 2003, San Jose, CA, USA. IEEE, 2003, pp. 57–60. DOI: https://doi.org/10.1109/CICC.2003.1249359.

- Kim, C. H.-I.; Soeleman, H.; Roy, K. “Ultra-low power DLMS adaptive filter for hearing aid applications,” IEEE Trans. Very Large Scale Integration (VLSI) Systems, Vol. 11, No. 6, P. 1058–1067, 2003. DOI: https://doi.org/10.1109/TVLSI.2003.819573.

- Kureshi, A. K.; Hasan, M. “DTMOS based low power high speed interconnects for FPGA,” J. Computers, Vol. 4, P. 921–926, 2009. DOI: http://doi.org/10.4304/jcp.4.10.921-926.

- Kumar, D.; Kumar, P.; Pattanaik, M. “Performance analysis of dynamic threshold MOS (DTMOS) based 4-input multiplexer switch for low power and high speed FPGA design,” Proc. of SBCCI’10, 6–9 Sept. 2010, Sao Paulo, Brazil, 2010. DOI: https://doi.org/10.1145/1854153.1854156.

- Singh, A. K. Digital VLSI Design, PHI publication, Eastern Economy Edition, 2011.

- Assaderaghi, F.; Sinitsky, D.; Parke, S. A.; Bokor, J.; Ko, P. K.; Hu, C. “Dynamic threshold-voltage MOSFET (DTMOS) for ultra-low voltage VLSI,” IEEE Trans. Electron Devices, Vol. 44, No. 3, P. 414–422, 1997. DOI: https://doi.org/10.1109/16.556151.

- Ghafari, P.; Anis, M.; Elmasry, M. “Impact of technology scaling on leakage reduction techniques,” Proc. of IEEE Northeast Workshop on Circuit and Systems, 5–8 Aug. 2007, Montreal, Que, Canada. IEEE, 2007, pp. 1405–1408. DOI: https://doi.org/10.1109/NEWCAS.2007.4488021.

- Weste, N. H.; Eshraghian, K.; Smith, M. J. Principles of CMOS VLSI Design: A Systems Perspective with Velirog/VHDL Manual, 2nd ed., Addison Wesley, 2000.

- Yu, W.; Hai, L.; Huazhong, Y.; Rong, L.; Hui, W. “Simultaneous fine-grain sleep transistor placement and sizing for leakage optimization,” Proc. of 7th Int. Symp. on Quality Electronic Design, 27–29 Mar. 2006, San Jose, CA, USA. IEEE, 2006. DOI: https://doi.org/10.1109/ISQED.2006.117.

- Augsburger, S.; Nigolic, B. “Combining dual-supply, dual-threshold and transistor sizing for power reduction,” Proc. of IEEE Int. Conf. on Computer Design: VLSI in Computers and Processors, 18 Sept. 2002, Freiberg, Germany. IEEE, 2002, pp. 316–321. DOI: https://doi.org/10.1109/ICCD.2002.1106788.

- Khandelwal, V.; Srivastava, A. “Leakage control through fine-grained placement and sizing of sleep transistors,” Proc. of IEEE/ACMInt. Conf. on Computer Aided Design, 7–11 Nov. 2004, San Jose, CA, USA. IEEE, 2004, pp. 533–536. DOI: https://doi.org/10.1109/ICCAD.2004.1382635.

- Singh, A. K.; Samanta, J. “Different physical effects in UDSM MOSFET for delay & power estimation: A review,” Proc. of IEEE Conf. on Electrical, Electronics and Computer Science, SCEECS, 1–2 May 2002, Bhopal, India. IEEE, 2002, pp. 1–5. DOI: https://doi.org/10.1109/SCEECS.2012.6184747.

- Mallik, A.; Chattopadhyay, A. “Tunnel field-effect transistors for analog/mixed-signal system-on-chip applications,” IEEE Trans. Electron Devices, Vol. 59, No. 4, P. 888–894, 2012. DOI: https://doi.org/10.1109/TED.2011.2181178.

- Chen, J.; Luo, J.; Wu, Q.; Chai, Z.; Yu, T.; Dong, Y.; Wang, X. “A tunnel diode body contact structure to suppress the floating-body effect in partially depleted SOI MOSFETs,” IEEE Electron Device Lett., Vol. 32, No. 10, P. 1346–1348, 2011. DOI: https://doi.org/10.1109/LED.2011.2162813.

- Jain, P.; Akashe, S. “Analysis of ATPMOS configurations-based 4x1 multiplexer with estimation of power and delay,” Int. J. Electronics, Vol. 101, No. 7, P. 1006–1018, 2014. DOI: https://doi.org/10.1080/00207217.2013.805391.

- Rajani, H. P.; Srimannarayan, K. “Novel sleep transistor techniques for low leakage power peripheral circuits,” Int. J. VLSI Design Commun. Syst., Vol. 3, No. 4, P. 81, 2012. DOI: http://doi.org/10.5121/vlsic.2012.3408.

- Sharma, V. K.; Soni, S. “Comparison among different CMOS inverters for low leakage at different technologies,” Int. J. Applied Engineering Research, Vol. 1, No. 2, P. 228, 2010. URI: http://ipublishing.co.in/jarvol1no12010/EIJAER1021.pdf.

- Rani, M. J.; Malarkann, S. “Leakage power reduction and analysis of CMOS sequential circuits,” Int. J. VLSI Design Commun. Syst., Vol. 3, No. 1, P. 13, 2012. DOI: http://doi.org/10.5121/vlsic.2012.3102.

- Lotze, N.; Manoli, Y. “A 62mV 0.13µm CMOS standard-cell-based design technique using Schmitt-trigger logic,” IEEE J. Solid State Circuits, Vol. 47, No. 1, P. 47–60, 2012. DOI: https://doi.org/10.1109/JSSC.2011.2167777.

- Kao, J. C.; Ma, W.-H.; Visvesh, S.; Papaefthymiou, M. “Energy-efficient low-latency 600 MHz FIR with high-overdrive charge-recovery logic,” IEEE Trans. Very Large Scale Integration (VLSI) Systems, Vol. 20, No. 6, P. 977–988, 2012. DOI: https://doi.org/10.1109/TVLSI.2011.2140346.

- Ho, Y.; Chang, C.; Su, C. “Design of a subthreshold-supply bootstrapped CMOS inverter based on an active leakage-current reduction technique,” IEEE Trans. Circuits and Systems II: Express Briefs, Vol. 59, No. 1, P. 55–59, 2012. DOI: https://doi.org/10.1109/TCSII.2011.2174674.

- Akashe, S.; Sharma, S. “Leakage current reduction techniques for 7T SRAM cell in 45 nm technology,” Wireless Pers. Commun., Vol. 71, No. 1, P. 123–136, 2013. DOI: https://doi.org/10.1007/s11277-012-0805-1.

- Soni, S.; Akashe, S. “Enhanced power gating schemes for low leakage power and low ground bounce noise in design of ring oscillator,” Wireless Pers. Commun., Vol. 80, No. 4, P. 1517–1533, 2015. DOI: https://doi.org/10.1007/s11277-014-2096-1.

##submission.downloads##

Опубліковано

2018-03-30

Як цитувати

Джеин, П., & Джоши, А. М. (2018). Анализ влияния расширенной конфигурации n-МОП транзистора на параметры 4x1 мультиплексора. Вісті вищих учбових закладів. Радіоелектроніка, 61(3), 163–172. https://doi.org/10.20535/S0021347018030044

Номер

Розділ

Оригінальні статті