Реализация комплексной цифровой системы ФАПЧ для фазового детектирования в программно определяемом радаре

DOI:

https://doi.org/10.20535/S0021347016040014Ключові слова:

программно определяемый радар, SDR, цифровая фазовая автоподстройка частоты, ФАПЧ, алгоритм CORDIC, фильтр BOXCAR, демодуляцияАнотація

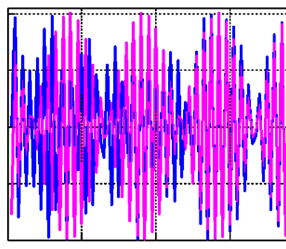

Программно определяемый радар SDR (software defined radar) представляет собой новейшее направление в разработке расширенных методик обработки сигнала радара для современных радиолокационных систем. SDR обеспечивает высокую гибкость перестройки структуры и быстрое макетирование на платформе FPGA (программируемая логическая интегральная схема, ПЛИС). Для осуществления обработки данных в реальном времени быстродействующего радара используется цифровой компьютер координационного вращения CORDIC (COordinate Rotation Digital Computer) в качестве основного процессорного элемента в комплексной цифровой системе фазовой автоподстройки частоты (ФАПЧ) для цифровой демодуляции принятого сигнала. Поскольку системы реального времени работают с высокими частотами дискретизации, выбрана конвейерная архитектура процессорного элемента CORDIC для обеспечения высокой скорости обработки (пропускной способности). Эта архитектура оптимизирована в отношении битовой длины для лучшей сходимости и повышения качества работы контура комплексной ФАПЧ первого порядка во время демодуляции. Узкополосный фильтр типа BOXCAR использован в качестве фильтра нижних частот в выходном каскаде детектора для улучшения извлечения информации из узких выборок при малой энергии сигнала без необходимости дополнительных затрат аппаратных средств. Приведены результаты моделирования в среде MATLAB для демонстрации эффективности этой конструкции интегральной схемы применительно к фазовому детектированию в радаре.Посилання

- High resolution software defined radar system for target detection / Sandra Costanzo, Francesco Spadafora, Antonio Borgia, Oswaldo Hugo Moreno, Antonio Costanzo, Giuseppe Di Massa // Advances in Information Systems and Tech. — 2013. — Vol. 206. — P. 997–1005. — DOI : http://dx.doi.org/10.1007/978-3-642-36981-0_94.

- Software defined radar platform testbed for micro-Doppler detection / In-Sang Woo, Jung-Soo Jung, Myeong-Seok Park, Young-Kil Kwag // Synthetic Aperture Radar : IEEE 5th Asia-Pacific Conf. APSAR, 1–4 Sept. 2015, Singapore : proc. — IEEE, 2015. — P. 50–53. — DOI : http://dx.doi.org/10.1109/APSAR.2015.7306152.

- Glance B. Digital phase demodulator / Bernard Glance // Bell System Tech. J. — Mar. 1971. — Vol. 50, No. 3. — P. 933–949. — DOI : http://dx.doi.org/10.1002/j.1538-7305.1971.tb01890.x.

- Kelly C. The digital phase-locked loop as a near-optimum FM demodulator / C. Kelly, S. Gupta // IEEE Trans. Commun. — Jun. 1972. — Vol. 20, No. 3. — P. 406–411. — DOI : http://dx.doi.org/10.1109/TCOM.1972.1091166.

- SQNR estimation of fixed-point DSP algorithms / Gabriel Caffarena, Carlos Carreras, Juan A. Lуpez, Бngel Fernбndez // EURASIP J. Advances Signal Process. — 2010. — DOI : http://dx.doi.org/10.1155/2010/171027.

- Volder J. E. The CORDIC trigonometric computing technique / Jack E. Volder // IRE Trans. Electronic Computers. — 1959. — Vol. EC-8, No. 3. — P. 330–334. — DOI : http://dx.doi.org/10.1109/TEC.1959.5222693.

- Hu Y. H. CORDIC-based VLSI architectures for digital signal processing / Y. H. Hu // IEEE Signal Processing Mag. — Jul. 1992. — Vol. 9, No. 3. — P. 16–35. — DOI : http://dx.doi.org/10.1109/79.143467.

- The use of CORDIC in software defined radios: a tutorial / J. Valls, T. Sansaloni, A. Perez-Pascual, V. Torres, V. Almenar // IEEE Commun. Magazine. — Sept. 2006. — Vol. 44, No. 9. — P. 46–50. — DOI : http://dx.doi.org/10.1109/79.143467.

- Hatai I. A new high-performance digital FM modulator and demodulator for software-defined radio and its FPGA implementation / Indranil Hatai, Indrajit Chakrabarti // Int. J. Reconfigurable Computing. — 2011. — Vol. 2011, No. 2. — P. 1–10. — DOI : http://dx.doi.org/10.1155/2011/342532.

- Zhang H. Software-defined six-port radar technique for precision range measurements / Hui Zhang, Lin Li, Ke Wu // IEEE Sensors J. — Oct. 2008. — Vol. 8, No. 10. — P. 1745–1751. — DOI : http://dx.doi.org/10.1109/JSEN.2008.2003304.

- Post correction of pipelined analog-digital converters based on input-dependent integral nonlinearity modeling / S. Medawar, P. Handel, N. Bjorsell, M. Jansson // IEEE Trans. Instrum., Meas. — Oct. 2011. — Vol. 60, No. 10. — P. 3342–3350. — DOI : http://dx.doi.org/10.1109/TIM.2011.2126870.

- Farina A. Effect of ADC and receiver saturation on adaptive spatial filtering of directional interference / A. Farina, L. Ortenzi // Signal Processing. — May 2003. — Vol. 83, No. 5. — P. 1065–1078. — DOI : http://dx.doi.org/10.1016/S0165-1684(02)00507-8.

- Liu Y. A modified CORDIC FPGA implementation for wave generation / Yidong Liu, Lihang Fan, Tieying Ma // Circuits, Syst. Signal Process. — 2014. — Vol. 33, No. 1. — P. 321–329. — DOI : http://dx.doi.org/10.1007/s00034-013-9638-8.

- Mandal A. Design of complex non-linear adaptive equalizer in mitigating severe intersymbol interferences / A. Mandal, R. Mishra // J. Signal Processing Systems. — 2015. — P. 1–12. — DOI : http://dx.doi.org/10.1007/s11265-015-1047-8.

- Mandal A. FPGA implementation of pipelined CORDIC for digital demodulation in FMCW radar / Amritakar Mandal, Rajesh Mishra // Infocommunications J. — 2013. — Vol. 5, No. 2. — P. 17–23. — URL : http://www.infocommunications.hu/documents/169298/393371/2013_2_3_Mandal.pdf.

- Hu Y. H. The quantization effects of the CORDIC algorithm / Y. H. Hu // IEEE Trans. Signal Processing. — Apr. 1992. — Vol. 40, No. 4. — P. 834–844. — DOI : http://dx.doi.org/10.1109/78.127956.

- Sung T.-Y. Fixed-point error analysis of CORDIC arithmetic for special-purpose signal processor / Tze-Yun Sung, Hsi-Chin Hsin // IEICE Trans. Fund. Elec., Commun. Computer Sci. — 2007. — Vol. E90-A, No. 9. — P. 2006–2013. — URL : http://search.ieice.org/bin/summary.php?id=e90-a_9_2006&category=A&year=2007&lang=E&abst=.

- Karimi-Ghartemani M. A magnitude/phase- locked loop system based on estimation of frequency and in-phase/quadrature-phase amplitudes / M. Karimi-Ghartemani, H. Karimi, M. R. Iravani // IEEE Trans. Ind. Electron. — Apr. 2004. — Vol. 51, No. 2. — P. 511–517. — DOI : http://dx.doi.org/10.1109/TIE.2004.825282.

- Нахмансон Г. С. Обнаружение фазоманипулированных сигналов с плавным изменением фазы при приеме на фоне шума / Г. С. Нахмансон, А. В. Суслин // Известия вузов. Радиоэлектроника. — 2012. — Т. 55, № 1. — С. 55–60. — Режим доступа : http://radio.kpi.ua/article/view/S0021347012010074.

- Vuori J. Implementation of a digital phase-locked loop using CORDIC algorithm / J. Vuori // Circuit and Systems : IEEE Int. Symp. ISCAS, 12–15 May 1996, Atlanta, USA : proc. — IEEE, 1996. — Vol. 4. — P. 164–167. — DOI : http://dx.doi.org/10.1109/ISCAS.1996.541925.

- Kumm M. An FPGA-based linear all-digital phase-locked loop / M. Kumm, H. Klingbeil, P. Zipf // IEEE Trans. Circuits Syst. I: Regular Papers. — Sept. 2010. — Vol. 57, No. 9. — P. 2487–2497. — DOI : http://dx.doi.org/10.1109/TCSI.2010.2046237.

- Mandal A. Design and implementation of digital demodulator for frequency modulated CW RADAR / A. Mandal, R. Mishra // IJE Trans. A: Basics. — Otc. 2014. — Vol. 27, No. 10. — P. 1581–1590. — URL : http://www.ije.ir/Vol27/No10/A/12.pdf.

- Babu B. S. Analogue-to-digital converter effects on airborne radar performance / B. S. Babu, C. M. Sorrentino // IEEE Radar Conf., 29–30 Mar. 1989, Dallas, TX : proc. — IEEE, 1989. — P. 56–61. — DOI : http://dx.doi.org/10.1109/NRC.1989.47615.

##submission.downloads##

Опубліковано

2016-04-20

Як цитувати

Мандал, А., Мишра, Р., & Нагар, М. Р. (2016). Реализация комплексной цифровой системы ФАПЧ для фазового детектирования в программно определяемом радаре. Вісті вищих учбових закладів. Радіоелектроніка, 59(4), 3–18. https://doi.org/10.20535/S0021347016040014

Номер

Розділ

Оригінальні статті