Усиливающая 3Т ячейка eDRAM памяти с улучшенными параметрами чтения и удержания данных

DOI:

https://doi.org/10.20535/S002134701603002XКлючові слова:

eDRAM, удержание данных, усиливающая 3Т ячейка, увеличенный запас хранения, мощность утечки, нанотехнологияАнотація

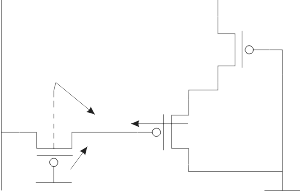

Представлена ячейка динамической оперативной памяти DRAM (Dynamic Random Access Memory) на трех транзисторах (3Т), с уменьшенными шумом, статической мощностью и напряжением удержания данных DRV (data retention voltage). Указанные параметры в предложенной ячейке улучшены путем подсоединения истока запоминающего элемента к RWL шине (Read Word Line) вместо напряжения питания. Как известно, потребляемая мощность играет важную роль при проектировании сверхбольших интегральных схем (СБИС) и входит в число основных проблем отрасли производства полупроводниковых кристаллов. С целью поддержания эффективности выполнения операции записи получено пониженное значение DRV и увеличено время хранения ячейки eDRAM при помощи разработанной схемы, названной «форсированной усиливающей 3Т ячейкой eDRAM-памяти». Предложенный тип ячейки eDRAM использует RWL шину посредством трех p-канальных MOS транзисторов (PMOS), вместо n-канальных MOS транзисторов (NMOS). PMOS транзисторы являются предпочтительными, поскольку обладают намного меньшим током утечки затвора, что обеспечивает лучшие результаты для удержания данных и увеличивает время хранения ячейки. Результаты проведенного моделирования получены с помощью программного пакета Cadence Virtuoso Tool при использовании 45 нм технологии для предложенной модели. На основании моделирования сделан вывод, что по сравнению с обычной усиливающей ячейкой eDRAM-памяти параметры предложенной ячейки существенно улучшены: статическая мощность составляет 0,767 пВт, напряжение DRV равно 142,009 мВ, шум составляет 8,421 нВ/Гц1/2.

Посилання

- Sze S. M. Physics of Semiconductor Devices / S. M. Sze. — 2nd ed. — New York: Wiley, 1981.

- Matick R. E. Logic-based eDRAM: Origins and rationale for use / R. E. Matick, S. E. Schuster // IBM J. Res. Develop. — Jan. 2005. — Vol. 49, No. 1. — P. 145–165. — DOI : http://dx.doi.org/10.1147/rd.491.0145.

- A 500 MHz random cycle, 1.5 ns latency, SOI embedded DRAM macro featuring a three-transistor micro sense amplifier / J. Barth, W. R. Reohr, P. Parries, G. Fredeman, J. Golz, S. E. Schuster, Richard E. Matick, H. Hunter, C. C. Tanner, J. Harig, H. Kim, B. A. Khan, J. Griesemer, R. P. Havreluk, K. Yanagisawa, T. Kirihata, S. S. Iyer // IEEE J. Solid-State Circuits. — Jan. 2008. — Vol. 43, No. 1. — P. 86–95. — DOI : http://dx.doi.org/10.1109/JSSC.2007.908006.

- Luk W. K. A 3-transistor DRAM cell with gated diode for enhanced speed and retention time / W. K. Luk, Jin Cai, R. H. Dennard, M. J. Immediato, S. V. Kosonocky // Proc. of IEEE Symp. on VLSI Circuits : Honolulu, HI : Digest of Technical Papers. — IEEE, 2006. — P. 184–185. — DOI : http://dx.doi.org/10.1109/VLSIC.2006.1705371.

- Chun K. C. A sub-0.9V logic-compatible embedded DRAM with boosted 3T gain cell, regulated bit-line write scheme and PVT-tracking read reference bias / Ki Chul Chun, P. Jain, Jung Hwa Lee, C. H. Kim // IEEE Symp. VLSI Circuits : 16–18 June 2009, Kyoto, Japan : proc. — IEEE, 2009. — P. 134–135. — URL : http://ieeexplore.ieee.org/xpl/login.jsp?tp=&arnumber=5205419&url=http%3A%2F%2Fieeexplore.ieee.org%2Fxpls%2Fabs_all.jsp%3Farnumber%3D5205419.

- Kiyoo Itoh B. S. Trends in megabit DRAM circuit design / B. S. Kiyoo Itoh // IEEE J. Solid-State Circuits. — Jun. 1990. — Vol. 25, No. 3. — P. 778–789. — DOI : http://dx.doi.org/10.1109/4.102676.

- Akashe S. A low leakage current power 45-nm CMOS SRAM / Shyam Akashe, Deepak Kumar Sinha, Sanjay Sharma // Indian J. Sci. Technol. — 2011. — Vol. 4, No. 4. — P. 440–442. — DOI : http://dx.doi.org/10.17485/ijst/2011/v4i4/30019.

- Shrivastava A. Low power analysis in single stage source coupled VCO with AVL technique using nanoscale CMOS technology / Akansha Shrivastava, Saurabh Khandelwal, Shyam Akashe // Engineering and Systems : IEEE Students Conf. SCES, 12–14 Apr. 2013, Allahabad, India. — IEEE, 2013. — P. 1–6. — DOI : http://dx.doi.org/10.1109/SCES.2013.6547488.

- Chandrakasan A. P. Low Power Digital CMOS Design / A. P. Chandrakasan, R. W. Brodersen. — Wiley–IEEE Press, Jan. 1998.

- Butts J. A. A static power model for architects / J. A. Butts, G. S. Sohi // Microarchitecture : 33rd Annual IEEE/ACM Int. Symp. MICRO-33, 10–13 Dec. 2000, Monterey, CA. — IEEE, 2000. — P. 191–201. — DOI : http://dx.doi.org/10.1109/MICRO.2000.898070.

- Seevinck E. Current-mode techniques for high-speed VLSI circuits with application to current sense amplifier for CMOS SRAM’s / E. Seevinck, P. J. van Beers, H. Ontrop // IEEE J. Solid-State Circuits. — Apr. 1991. — Vol. 26, No. 4. — P. 525–536. — DOI : http://dx.doi.org/10.1109/4.75050.

- A 1.8-V 128-Mb mobile DRAM with double boosting pump, hybrid current sense amplifier, and dual-referenced adjustment scheme for temperature sensor / Jae-Yoon Sim, Hongil Yoon, Ki-Chul Chun, Hyun-Seok Lee, Sang-Pyo Hong, Kyu-Chan Lee, Jei-Hwan Yoo, Dong-Il Seo, Soo-In Cho // IEEE J. Solid-State Circuits. — Apr. 2003. — Vol. 38, No. 4. — P. 631–640. — DOI : http://dx.doi.org/10.1109/JSSC.2003.809514.