Анализ методов уменьшения тока и мощности утечки в ячейке SRAM на основе FinFET транзисторов

DOI:

https://doi.org/10.20535/S0021347015070031Ключові слова:

ток утечки, потребляемая мощность, статическое оперативное запоминающее устройство, ОЗУ, под-пороговый ток утечки, ток утечки затвора, FinFETАнотація

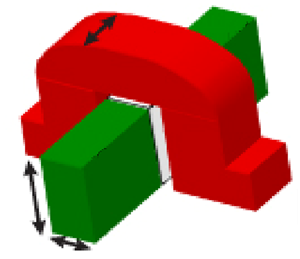

Предложена ячейка статического оперативного запоминающего устройства SRAM (Static Random Access Memory) на основе 6 полевых транзисторов с вертикально расположенным затвором (FinFET транзистор). FinFET устройства использованы для улучшения рабочих характеристик, уменьшения тока и мощности утечки. Цель этой статьи заключается в снижении тока и мощности утечки ячейки SRAM на основе 6 FinFET транзисторов, используя различные методы 45-нм технологии. Разработана ячейка SRAM на основе 6 FinFET транзисторов и проведен анализ тока и мощности утечки. При разработке устройств памяти с низким потреблением наиболее важной проблемой является минимизация под-порогового тока утечки и тока утечки затвора. Эта работа предлагает метод, основанный на одновременной установке соответствующих значений порогового напряжения, толщины оксидного слоя затвора и напряжения источника питания с целью минимизации под-порогового тока утечки и тока утечки затвора в ячейке SRAM на основе 6 транзисторов. Результаты проведенного моделирования получены с помощью программы Cadence Virtuoso для 45-нм технологии.Посилання

- A 130 nm generation logic technology featuring 70 nm transistors, dual Vt transistors and 6 layers of Cu interconnects / S. Tyagi, M. Alavi, R. Bigwood, T. Bramblett, J. Brandenburg, W. Chen, B. Crew, M. Hussein, P. Jacob, C. Kenyon, C. Lo, B. McIntyre, Z. Ma, P. Moon, P. Nguyen, L. Rumaner, R. Schweinfurth, S. Sivakumar, M. Stettler, S. Thompson, B. Tufts, J. Xu, S. Yang, M. Bohr // Electron Devices Meeting : Int. Tech. Dig. IEDM'00, 10–13 Dec. 2000, San Francisco, CA, USA : proc. — IEEE, 2000. — P. 567–570. — DOI : http://dx.doi.org/10.1109/IEDM.2000.904383.

- Shukla N. Kr. Design and analysis of a novel low-power SRAM bit-cell structure at deep-sub-micron CMOS technology for mobile multimedia applications / Neeraj Kr. Shukla, R. K. Singh, Manisha Pattanaik // Int. J. Advanced Comput. Sci. Appl. — 2011. — Vol. 2, No. 5. — P. 43–49. — DOI : http://dx.doi.org/10.14569/IJACSA.2011.020507.

- Amelifard B. Reducing the sub-threshold and gate-tunneling leakage of SRAM cells using dual-Vt and dual-Tox assignment / B. Amelifard, F. Fallah, M. Pedram // Design Automation and Test in Europe : IEEE Int. Conf. DATE'06, 6–10 March 2006, Munich : proc. — IEEE, 2006. — Vol. 1. — P. 1–6. — DOI : http://dx.doi.org/10.1109/DATE.2006.243896.

- Anand P. R. Reduce leakage currents in low power SRAM cell structures / P. R. Anand, P. C. Sekhar // Parallel and Distributed Processing with Applications Workshops : Ninth IEEE Int. Symp. ISPAW, 26–28 May 2011, Busan : proc. — IEEE, 2011. — P. 33–38. — DOI : http://dx.doi.org/10.1109/ISPAW.2011.62.

- Shukla N. Kr. Analysis of gate leakage current in IP3 SRAM bit-cell under temperature variations in DSM technology / Neeraj Kr. Shukla, R. K. Singh, Manisha Pattanaik // Int. J. Eng. Technol. — 2012. — Vol. 4, No. 1. — P. 67–71. — DOI : http://dx.doi.org/10.7763/IJET.2012.V4.320.

- Leakage current reduction in 6T single cell SRAM at 90nm technology / S. Birla, N. Kr. Shukla, D. Mukherjee, R. K. Singh // Advances in Computer Engineering : IEEE Int. Conf. ACE, 20–21 June 2010, Bangalore, Karnataka, India : proc. — IEEE, 2010. — P. 292–294. — DOI : http://dx.doi.org/10.1109/ACE.2010.42.

- Leakage power reduction techniques of 55 nm SRAM cells / Li-Jun Zhang, Chen Wu, Ya-Qi Ma, Jian-Bin Zheng, Ling-Feng Mao // IETE Technical Review. — 2011. — Vol. 28, No. 2. — P. 315–318.

- Kang S. M. CMOS digital integrated circuits II / S. M. Kang, Y. Leblebici. — TMH publishing company limited, 2007.

- Kanda K. 90% write power-saving SRAM using sense-amplifying memory cell / K. Kanda, H. Sadaaki, T. Sakurai // IEEE J. Solid-State Circuits. — Jun. 2004. — Vol. 39, No. 6. — P. 927–933. — DOI : http://dx.doi.org/10.1109/JSSC.2004.827793.

- Agarwal A. DRG-cache: a data retention gated-ground cache for low power / A. Agarwal, H. Li, K. Roy // Design Automation Conf. : 39th Int. Conf., 2002 : proc. — IEEE, 2002. — P. 473–478. — DOI : http://dx.doi.org/10.1109/DAC.2002.1012671.

- Agarwal A. A single-Vt low-leakage gated-ground cache for deep submicron / A. Agarwal, Hai Li, K. Roy // IEEE J. Solid-State Circuits. — Feb. 2003. — Vol. 38, No. 2. — P. 319–328. — DOI : http://dx.doi.org/10.1109/JSSC.2002.807414.

- Modeling and simulation of high speed 8T SRAM cell / Raj Johri, Ravindra Singh Kushwah, Raghvendra Singh, Shyam Akashe // Bio-Inspired Computing: Theories and Applications. Advances in Intelligent Systems and Computing : Seventh Int. Conf. BIC-TA, 2012 : proc. — 2013. — Vol. 2. — P. 245–251. — DOI : http://dx.doi.org/10.1007/978-81-322-1041-2_21.

- Sheikh F. The impact of device-width quantization on digital circuit design using FinFET structures / Farhana Sheikh, Vidya Varadarajan // Proc. EE241 Spring. — 2004. — P. 1–6.

- SRAM leakage suppression by minimizing standby supply voltage / Hulfang Qin, Yu Cao, D. Markovic, A. Vladimirescu, J. Rabaey // Quality Electronic Design : IEEE Int. Symp., 2004 : proc. — IEEE, 2004. — P. 55–60. — DOI : http://dx.doi.org/10.1109/ISQED.2004.1283650.

##submission.downloads##

Опубліковано

2015-07-23

Як цитувати

Кушвах, Р. С., & Сикарвар, В. (2015). Анализ методов уменьшения тока и мощности утечки в ячейке SRAM на основе FinFET транзисторов. Вісті вищих учбових закладів. Радіоелектроніка, 58(7), 26–39. https://doi.org/10.20535/S0021347015070031

Номер

Розділ

Оригінальні статті