Исследование линейности интермодуляционной характеристики МШУ для беспроводной локальной сети при оптимальном смещении

DOI:

https://doi.org/10.20535/S0021347015050015Ключові слова:

нелинейная схема, двойной затвор, кремний-на-диэлектрике, малошумящий усилитель, МШУ, малая мощность, SOIАнотація

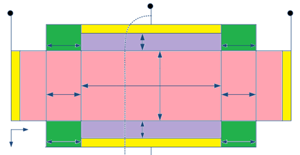

В работе представлено исследование влияния эффекта изменения технологических параметров новых полевых МОП-транзисторов со структурой SOI (Silicon–on–Insulator) и частичным перекрытием затвора MOSFET (metal–oxide–semiconductor field–effect transistor) на линейность каскодного малошумящего усилителя (МШУ), применяющегося в беспроводных локальных сетях (WLAN). С помощью количественной оценки линейности МШУ посредством точки пересечения третьего порядка (IP3) в работе даны рекомендации по определению оптимального размера спейсера (spacer) s, толщины пленки TSi, градиента легирующей примеси d и длины затвора LG полевого транзистора с частичным перекрытием затвора для повышения линейности МШУ. На основе нового показателя качества МШУ (FoMLNA), включающего коэффициент усиления сигнала по мощности G, показатель IP3, коэффициент шума NF и потребляемую мощность Pdc, установлено, что показатель качества FoMLNA для конфигурации с двойным затвором (DG) намного выше, чем для конфигурации с одиночным затвором (SG) при оптимальном напряжении смещения затвора VOD = 75 мВ. Это обусловлено комбинированным эффектом повышения коэффициента усиления G и показателя IP3 в конфигурации с двойным затвором. При сравнении с доступными экспериментальными данными для 0,18 мкм балк-технологии установлено, что при использовании новых полевых МОП-транзисторов со структурой SOI и частичным перекрытием затвора с длиной затвора LG = 60 нм (эффективная длина затвора Leff = 92 нм) оптимально спроектированный МШУ с оптимальным смещением обеспечивает двукратное повышение предлагаемого показателя качества FoMLNA. При оптимальном смещении МШУ получены следующие показатели: коэффициент шума NF ~ 2,27 дБ, IP3 ~ +7,75 дБм, G ~ 20,86 дБ, потребляемая мощность 2,5 мВт.

Посилання

- A 5.8-GHz two-stage high-linearity low-voltage low noise amplifier in a 0.35-μm CMOS technology / Ren-Chieh Liu, Chung-Rung Lee, Huei Wang, Chorng-Kuang Wang // Radio Frequency Integrated Circuits : IEEE RFIC Symp., 3–4 June 2002, Seattle, WA, USA : proc. — IEEE, 2002. — P. 221–224. — DOI : http://dx.doi.org/10.1109/RFIC.2002.1012036.

- Zhang H. Linearization Techniques for CMOS low noise amplifiers: A tutorial / Heng Zhang, Edgar Sanchez-Sinencio // IEEE Trans. Circuits Syst. I: Regular Papers. — Jan. 2011. — Vol. 58, No. 1. — P. 22–36. — DOI : http://dx.doi.org/10.1109/TCSI.2010.2055353.

- Optimally designed moderately inverted double gate SOI MOSFETs for low-power RFICs / Dipankar Ghosh, Mukta Singh Parihar, G. Alastair Armstrong, Abhinav Kranti // Semicond. Sci. Tech. — 2012. — Vol. 27, No. 12. — P. 125004. — DOI : http://dx.doi.org/10.1088/0268-1242/27/12/125004.

- Park S. Design of a 1.8 GHz low-noise amplifier for RF front-end in 0.8 μm CMOS technology / Sungkyung Park, Wonchan Kim // IEEE Trans. Cons. Electron. — Feb. 2001. — Vol. 47, No. 1. — P. 10–15. — DOI : http://dx.doi.org/10.1109/30.920413.

- Kaya S. Optimization of RF linearity in DG-MOSFETs / Savas Kaya, Wei Ma // IEEE Electron Device Lett. — May 2004. — Vol. 25, No. 5. — P. 308–310. — DOI : http://dx.doi.org/10.1109/LED.2004.826539.

- Kranti A. Nonclassical channel design in MOSFETs for improving OTA gain-bandwidth trade-off / Abhinav Kranti, G. A. Armstrong // IEEE Trans. Circuits Syst. I: Regular Papers. — Dec. 2010. — Vol. 57, No. 12. — P. 3048–3054. — DOI : http://dx.doi.org/10.1109/TCSI.2010.2071470.

- Lee T.-Y. High frequency characterization and modelling of distortion behaviour of MOSFETs for RF IC design / Tzung-Yin Lee, Yuhua Cheng // IEEE J. Solid-State Circuits. — Sept. 2004. — Vol. 39, No. 9. — P. 1407–1414. — DOI : http://dx.doi.org/10.1109/JSSC.2004.829376.

- Kranti A. Gate length scaling and microwave performance of double gate nanotransistors / Abhinav Kranti, Tsung Ming Chung, Jean-Pierre Raskin // Int. J. Nanosci. — Dec. 2005. — Vol. 4, No. 5–6. — P. 1021–1024. — DOI : http://dx.doi.org/10.1142/S0219581X05004005.

- Razavi B. RF Micro-Electronics / B. Razavi. — Prentice-Hall, 1998.

- RF distortion characterisation of sub-micron CMOS / L. F. Tiemeijer, R. van Langevelde, O. Gaillard, R. J. Havens, P. G. M. Baltus, P. H. Woerlee, D. B. M. Klaassen // Solid-State Device Research : 30th European Conf., 11–13 Sept. 2000 : proc. — IEEE, 2000. — P. 464–467. — DOI : http://dx.doi.org/10.1109/ESSDERC.2000.194815.

- Alam M. S. Investigation of gate underlap design on linearity of operational transconductance amplifier / M. S. Alam, A. Kranti, G. A. Armstrong // Engineering and Computer Science : World Congress WCECS 2010, October 20–22, 2010, San Francisco, USA. — IEEE, 2010. — Vol. 2.

- Impact of high-κ offset spacer in 65-nm node SOI devices / Ming-Wen Ma, Chien-Hung Wu, Tsung-Yu Yang, Kuo-Hsing Kao, Woei-Cherng Wu, Shui-Jinn Wang, Tien-Sheng Chao, Tan-Fu Lei // IEEE Electron Device Lett. — Mar. 2007. — Vol. 28, No. 3. — P. 238–241. — DOI : http://dx.doi.org/10.1109/LED.2007.891282.

- Non-linearity analysis of FinFETs / A. Cerdeira, M. Aleman, V. Kilchitska, N. Collaert, K. de Meyer, D. Flandre // Devices, Circuits and Systems : 6th Int. Caribbean Conf., 26–28 April 2006, Playa del Carmen : proc. — IEEE, 2006. — P. 9–12. — DOI : http://dx.doi.org/10.1109/ICCDCS.2006.250827.

- Park J.-T. Multiple-gate SOI MOSFETs: device design guidelines / Jong-Tae Park, Jean-Pierre Colinge // IEEE Trans. Electron Devices. — Dec. 2002. — Vol. 49, No. 12. — P. 2222–2229. — DOI : http://dx.doi.org/10.1109/TED.2002.805634.

- International Technology Roadmap for Semiconductors. 2011 edition.

- Silvaco ATLAS-2011, www.silvaco.com.

- Wong H. Y. The gate misalignment effects of the sub-threshold characteristics of sub-100 nm DG-MOSFETs / Hiu Yung Wong, Kyoungsub Shin, M. Chan // Electron Device Meeting : IEEE Hong Kong Meeting, 2002 : proc. — IEEE, 2002. — P. 91–94. — DOI : http://dx.doi.org/10.1109/HKEDM.2002.1029164.

- Advanced Design System (ADS) 2012, www.agilent.com.

- Lee T. H. The design of CMOS radio-frequency integrated circuits / T. H. Lee. — UK Cambridge University Press, 1998.

- Arora R. Operating voltage constraints in 45-nm SOI nMOSFETs and cascode cores / Rajan Arora, John D. Cressler // IEEE Trans. Electron Devices. — Jan. 2013. — Vol. 60, No. 1. — P. 132–139. — DOI : http://dx.doi.org/10.1109/TED.2012.2227967.

- Wang Y. S. 5.7 GHz low-power variable-gain LNA in 0.18 µm CMOS / Y. S. Wang, L.-H. Lu // Electron. Lett. — 20 Jan. 2005. — Vol. 41, No. 2. — P. 66–68. — DOI : http://dx.doi.org/10.1049/el:20057230.

- Kwon I. An accurate behavioral model for RF MOSFET linearity analysis / Ickjin Kwon, Kwyro Lee // IEEE Microwave Wireless Compon. Lett. — Dec. 2007. — Vol. 17, No. 12. — P. 897–899. — DOI : http://dx.doi.org/10.1109/LMWC.2007.910518.

- Baki R. A. Distortion in RF CMOS short-channel low-noise amplifiers / Rola A. Baki, Tommy K. K. Tsang, Mourad N. El-Gamal // IEEE Trans. Microwave Theory Tech. — Jan. 2006. — Vol. 54, No. 1. — P. 46–56. — DOI : http://dx.doi.org/10.1109/TMTT.2005.860897.

- Pedro J. C. Intermodulation Distortion in Microwave and Wireless Circuits / Jose Carlos Pedro, Nuno Borges Carvalho. — Artech House, Inc., 2003. — 450 p.

- Design considerations for fully depleted SOI transistors in the 25–50 nm gate length regime / R. J. Luyken, T. Schulz, J. Hartwich, L. Dreeskornfeld, M. Stadele, W. Rosner // Solid-State Electron. — July 2003. — Vol. 47, No. 7. — P. 1199–1203. — DOI : http://dx.doi.org/10.1016/S0038-1101(03)00038-8.

- Kang S. Linearity analysis of CMOS for RF application / Sanghoon Kang, Byounggi Choi, Bumman Kim // IEEE Trans. Microwave Theory Tech. — Mar. 2003. — Vol. 51, No. 3. — P. 972–977. — DOI : http://dx.doi.org/10.1109/TMTT.2003.808709.

- Toole B. RF circuit implications of moderate inversion enhanced linear region in MOSFETs / B. Toole, C. Plett, M. Cloutier // IEEE Trans. Circuits Syst. I: Regular Papers. — Feb. 2004. — Vol. 51, No. 2. — P. 319–328. — DOI : http://dx.doi.org/10.1109/TCSI.2003.822400.

- A simple figure of merit of RF MOSFET for low noise amplifier design / Ickhyun Song, Jongwook Jeon, Hee-Sauk Jhon, Junsoo Kim, Byung-Gook Park, Jong Duk Lee, Hyungcheol Shin // IEEE Electron Device Lett. — Dec. 2008. — Vol. 29, No. 12. — P. 1380–1382. — DOI : http://dx.doi.org/10.1109/LED.2008.2006863.

- High gain, low noise cascode LNA with RF amplifier at 5.8 GHz using T-matching networks / Abu Bakar Ibrahim, Abdul Rani Othman, Mohd Nor Hussain, Mohammad Syahrir Johal // Advancements in Electronics and Power Engineering : 2nd Int. Conf. ICAEPE’2012, June 30–July, 2012, Bali : proc. — URL : http://www.academia.edu/3121327/high_gain_low_noise_cascode_LNA_with_RF_amplifier_at_5.8GHz_using_T-matching_network.

- RF noise of 65-nm MOSFETs in the weak-to-moderate-inversion region / Jinglin Shi, Yong Zhong Xiong, Kai Kang, Lan Nan, Fujiang Lin // IEEE Electron Device Lett. — Feb. 2009. — Vol. 30, No. 2. — P. 185–188. — DOI : http://dx.doi.org/10.1109/LED.2008.2010464.

- Noise modeling for RF CMOS circuit simulation / Andries J. Scholten, Luuk F. Tiemeijer, Ronald van Langevelde, Ramon J. Havens, Adrie T. A. Zegers-van Duijnhoven, Vincent C. Venezia // IEEE Trans. Electron Devices. — Mar. 2003. — Vol. 50, No. 3. — P. 218–232. — DOI : http://dx.doi.org/10.1109/TED.2003.810480.