Сравнительный анализ схем КМОП сумматоров на 10 транзисторах

DOI:

https://doi.org/10.20535/S0021347014090040Ключові слова:

полный одноразрядный сумматор, логическая функция, КМОП схемаАнотація

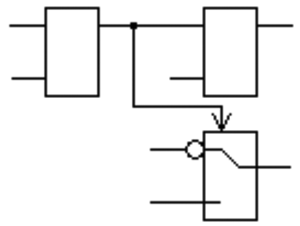

Развитие устройств цифровой обработки сигналов привело к появлению ряда КМОП схемотехнических решений арифметических и логических блоков с малым числом транзисторов. В данной работе предложена классификация полных одноразрядных КМОП сумматоров, схемы которых состоят из 10 транзисторов. На основе результатов схемотехнического моделирования для 0,18 мкм МОП технологии проведено сравнение основных характеристик сумматоров и выделены наиболее перспективные реализации.

Посилання

- Yano K. A 3.8-ns CMOS 16ґ16-b multiplier using complementary pass-transistor logic / K. Yano, T. Yamanaka, T. Nishida, M. Saito, K. Shimohigashi, A. Shimizu // IEEE J. Solid-State Circuits. — Apr. 1990. — Vol. 25, No. 2. — P. 388–395. — DOI : http://dx.doi.org/10.1109/4.52161.

- Weste N. H. E. CMOS VLSI Design: A Circuits and Systems Perspective / N. H. E. Weste, D. Harris. — Pearson Education, 2005. — 967 p.

- Zimmermann R. Low-power logic styles: CMOS versus pass-transistor logic / Reto Zimmermann, Wolfgang Fichtner // IEEE J. Solid-State Circuits. — Jul. 1997. — Vol. 32, No. 7. — P. 1079–1090. — DOI : http://dx.doi.org/10.1109/4.597298.

- Mahmoud H. A. A 10-transistor low-power high-speed full adder cell / H. A. Mahmoud, M. A. Bayoumi // Circuits and Systems : IEEE Int. Symp. ISCAS, Jun. 1999, Orlando, FL : proc. — IEEE, 1999. — Vol. 1. — P. 43–46. — DOI : http://dx.doi.org/10.1109/ISCAS.1999.777801.

- Shalem R. A novel low power energy recovery full adder cell / R. Shalem, E. John, L. K. John // VLSI : Proc. 9th Great Lakes Symp., 1999. — P. 380–383.

- Junming L. A novel 10-transistor low-power high-speed full adder cell / Lu Junming, Shu Yan, Lin Zhenghui, Wang Ling // Solid-State and Integrated-Circuit Technology : 6th Int. Conf., 22–25 Oct. 2001 : proc. — IEEE, 2001. — Vol. 2. — P. 1155–1158. — DOI : http://dx.doi.org/10.1109/ICSICT.2001.982104.

- Fayed A. A. A low power 10-transistor full adder cell for embedded architectures / A. A. Fayed, M. A. Bayoumi // Circuits and Systems : IEEE Int. Symp. ISCAS, 6–9 May 2001, Sydney, NSW : proc. — IEEE, 2001. — Vol. 4. — P. 226–229. — DOI : http://dx.doi.org/10.1109/ISCAS.2001.922213.

- Bui H. T. Design and analysis of low-power 10-transistor full adders using novel XOR-XNOR gates / Hung Tien Bui, Yuke Wang, Yingtao Jiang // IEEE Trans. Circuits Syst. II: Analog Digital Signal Process. — Jan. 2002. — Vol. 49, No. 1. — P. 25–30. — DOI : http://dx.doi.org/10.1109/82.996055.

- Vasefi F. Low power n-bit adders and multiplier using lowest-number-of-transistor 1-bit adders / Fartash Vasefi, Z. Abid // Electrical and Computer Engineering : Canadian Conf., 1–4 May 2005, Saskatoon, Sask. : proc. — IEEE, 2005. — P. 1731–1734. — DOI : http://dx.doi.org/10.1109/CCECE.2005.1557317.

- Lee P.-M. Novel 10-T full adders realized by GDI structure / Po-Ming Lee, Chia-Hao Hsu, Yun-Hsiun Hung // Integrated Circuits : Int. Symp. ISIC, 26–28 Sept. 2007, Singapore : proc. — IEEE, 2007. — P. 115–118. — DOI : http://dx.doi.org/10.1109/ISICIR.2007.4441810.

- Lin J.-F. Low-power and low-complexity full adder design for wireless base band application / Jin-Fa Lin, Ming-Hwa Sheu, Yin-Tsung Hwang // Communications, Circuits and Systems : Int. Conf., 25–28 June 2006, Guilin : proc. — IEEE, 2006. — Vol. 4. — P. 2337–2341. — DOI : http://dx.doi.org/10.1109/ICCCAS.2006.285145.

- Lin J.-F. A novel high-speed and energy efficient 10-transistor full adder design / Jin-Fa Lin, Yin-Tsung Hwang, Ming-Hwa Sheu, Cheng-Che Ho // IEEE Trans. Circuits Syst. I: Regular Papers. — May 2007. — Vol. 54, No. 5. — P. 1050–1059. — DOI : http://dx.doi.org/10.1109/TCSI.2007.895509.

- Lin J.-F. Low power 10-transistor full adder design based on degenerate pass transistor logic / Jin-Fa Lin, Yin-Tsung Hwang, Ming-Hwa Sheu // Circuits and Systems : IEEE Int. Symp. ISCAS, 20–23 May 2012, Seoul : proc. — IEEE, 2012. — P. 496–499. — DOI : http://dx.doi.org/10.1109/ISCAS.2012.6272074.

- Wairya S. Comparative performance analysis of XOR-XNOR function based high-speed CMOS full adder circuits for low voltage VLSI design / Subodh Wairya, Rajendra Kumar Nagaria, Sudarshan Tiwari // Int. J. VLSI design & Commun. Syst. — 2012. — Vol. 3, No. 2. — P. 221–242. — URL : http://airccse.org/journal/vlsi/papers/3212vlsics19.pdf.

- Wang J.-M. New efficient designs for XOR and XNOR functions on the transistor level / Jyh-Ming Wang, Sung-Chuan Fang, Wu-Shiung Feng // IEEE J. Solid-State Circuits. — Jul. 1994. — Vol. 29, No. 7. — P. 780–786. — DOI : http://dx.doi.org/10.1109/4.303715.

- Vesterbacka M. A new six-transistor CMOS XOR circuit with complementary output / M. Vesterbacka // Circuits and Systems : 42nd Midwest Symp., 1999, Las Cruces, NM : proc. — IEEE, 1999. — Vol. 2. — P. 796–799. — DOI : http://dx.doi.org/10.1109/MWSCAS.1999.867755.

- Морозов Д. В. Схемотехника современных цифровых схем с низкой потребляемой мощностью / Д. В. Морозов // Научно-технические ведомости СПбГПУ. Информатика. Телекоммуникации. Управление. — 2008. — Т. 3, № 60. — С. 111–116.

- Морозов Д. В. Схемотехническое решение одноразрядного двоичного КМОП сумматора / Д. В. Морозов, М. М. Пилипко // Микроэлектроника. — 2013. — Т. 42, № 2. — С. 146. — DOI : http://dx.doi.org/10.7868/S0544126913020099.

##submission.downloads##

Опубліковано

2014-09-11

Як цитувати

Пилипко, М. М., & Морозов, Д. В. (2014). Сравнительный анализ схем КМОП сумматоров на 10 транзисторах. Вісті вищих учбових закладів. Радіоелектроніка, 57(9), 42–54. https://doi.org/10.20535/S0021347014090040

Номер

Розділ

Оригінальні статті