Анализ и проектирование SRAM ячейки с низкой потребляемой мощностью на базе FinFET с независимыми затворами

DOI:

https://doi.org/10.20535/S0021347013090021Ключові слова:

КМОП, оперативная память, потребляемая мощность, FinFET, SRAM, MOSFETАнотація

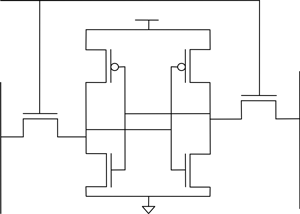

Масштабирование объемных МОП структур в нано микросхемах приводит к значительным проблемам из-за укороченных канальных эффектов, вызывающих рост утечек. Технология FinFET стала наиболее перспективной заменой объемной КМОП благодаря уменьшению эффектов короткого канала. Двух-затворный FinFET (dual-gate или DG FinFET) может быть спроектирован или путем соединения затворов для оптимизации характеристик, или оба затвора могут управляться независимо для уменьшения токов утечки и потребляемой мощности. Шести-транзисторная SRAM ячейка, основанная на FinFET с независимыми затворами IG (independent-gate), описанная в данной работе, обеспечивает одновременное уменьшение потребляемой мощности в активном режиме и режиме ожидания. В работе рассмотрена FinFET технология с независимыми затворами, так как она по сравнению с другими обеспечивает меньшее потребление мощности, меньшую площадь устройства и сравнительно небольшую задержку. Проведено сравнение токов утечки и потребляемой мощности FinFET с независимыми затворами и FinFET SRAM ячейки с соединенными затворами. Для рассматриваемых SRAM ячеек проведена оценка вносимой задержки. Кроме того, к FinFET 6T SRAM ячейке с независимыми затворами применена методика уменьшения утечек.

Посилання

- Device scaling limits of Si MOSFETs and their application dependencies / D. J. Frank, R. H. Dennard, E. Nowak, P. M. Solomon, Yuan Taur, Hen-Sum Philip Wong // Proc. IEEE. — Mar. 2001. — Vol. 89, No. 3. — P. 259–288. — doi : http://dx.doi.org/10.1109/5.915374">10.1109/5.915374.

- Kursun V. Multi-Voltage CMOS Circuit Design / V. Kursun and E. G. Friedman. — Hoboken, NJ : Wiley, 2006. — 242 p.

- Fried D. M. The Design, Fabrication and Characterization of Independent-Gate Finfets / D. M. Fried. — Cornell University, 2004. — 184 p.

- Rostami M. Novel dual-Vth independent-gate FinFET circuits / M. Rostami and K. Mohanram // Design Automation Conf. (ASP-DAC) : 15th IEEE Conf., 18–21 Jan. 2010, Asia and South Pasific. — 2010. — P. 867–872. — doi : http://dx.doi.org/10.1109/ASPDAC.2010.5419680">10.1109/ASPDAC.2010.5419680.

- Chin E. Design trade-offs of a 6T FinFET SRAM cell in the presence of variations / E. Chin, M. Dunga, B. Nikolic // IEEE. Symp. VLSI Circuits. — 2006. — P. 445–449.

- Tawfik S. A. Portfolio of FinFET memories: Innovative techniques for an emerging technology / S. A. Tawfik and Volkan Kursun // SoC Design Conf. : IEEE Int. Conf. ISOCC’08, 24–25 Nov. 2008, Busan. — 2008. — Vol. 1. — P. I-101–I-104. — doi : http://dx.doi.org/10.1109/SOCDC.2008.4815583">10.1109/SOCDC.2008.4815583.

- Tawfik Sh. A. Low power and stable FinFET SRAM with static independent gate bias for enhanced integration density / Sherif A. Tawfik and V. Kursun // Electronics, Circuits and Systems : 14th IEEE Int. Conf., ICECS 2007, 11–14 Dec. 2007, Marrakech. — 2007. — P. 443–446. — doi : http://dx.doi.org/10.1109/ICECS.2007.4511025">10.1109/ICECS.2007.4511025.

- Raj B. Nanoscale FinFET based SRAM cell design: Analysis of performance metric, process variation, underlapped FinFET and temperature effect / B. Raj, A. K. Saxena, S. Dasgupta // IEEE Circuits and Systems Magazine. — 2001. — Vol. 11, No. 3. — P. 38–50. — doi : http://dx.doi.org/10.1109/MCAS.2011.942068">10.1109/MCAS.2011.942068.

- Nirmal, Nand gate using FinFET for nanoscale technology / Nirmal, V. Kumar, S. Jabaraj // Int. J. Eng. Sci. Technol.. — May 2010. — Vol. 2, No. 5. — P. 1351–1358. — http://www.ijest.info/docs/IJEST10-02-05-10.pdf"> http://www.ijest.info/docs/IJEST10-02-05-10.pdf.

- Sikarwar V. Optimization of leakage current in SRAM cell using shorted gate DG FinFET / V. Sikarwar, S. Khandelwal, S. Akashe // Advanced Computing and Communication Technologies (ACCT) : 3rd IEEE Int. Conf., 6–7 Apr. 2013, Rohtak. — 2013. — P. 166–170. — doi : http://dx.doi.org/10.1109/ACCT.2013.41">10.1109/ACCT.2013.41.

- Akashe S. A low-leakage current power 45-nm CMOS SRAM / S. Akashe, D. K. Sinha, S. Sharma // Indian J. Sci. Technol. — 2011. — Vol. 4, No. 4. — P. 440–442. — http://www.indjst.org/index.php/indjst/article/view/30019"> http://www.indjst.org/index.php/indjst/article/view/30019.

- Rasouli S. H. Design optimization of FinFET domino logic considering the width quantization property / S. H. Rasouli, H. F. Dadgour, K. Endo, H. Koike, K. Banerjee // IEEE Trans. Electron Devices. — Nov. 2010. — Vol. 57, No. 11. — P. 2934–2943. — doi : http://dx.doi.org/10.1109/TED.2010.2076374">10.1109/TED.2010.2076374.

- Koh S.-M. Contact technology for strained nFinFETs with silicon-carbon source/drain stressors featuring sulfur implant and segregation / Shao-Ming Koh, G. S. Samudra, Yee-Chia Yeo // IEEE Trans. Electron Devices. — Apr. 2012. — Vol. 59, No. 4. — P. 1046–1055. — doi : http://dx.doi.org/10.1109/TED.2012.2185799">10.1109/TED.2012.2185799.