Усиливающая 3Т ячейка eDRAM памяти с улучшенными параметрами чтения и удержания данных

DOI:

https://doi.org/10.20535/S002134701603002XКлючові слова:

eDRAM, удержание данных, усиливающая 3Т ячейка, увеличенный запас хранения, мощность утечки, нанотехнологияАнотація

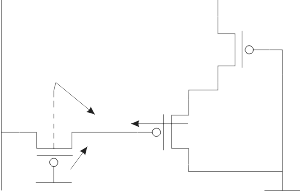

Представлена ячейка динамической оперативной памяти DRAM (Dynamic Random Access Memory) на трех транзисторах (3Т), с уменьшенными шумом, статической мощностью и напряжением удержания данных DRV (data retention voltage). Указанные параметры в предложенной ячейке улучшены путем подсоединения истока запоминающего элемента к RWL шине (Read Word Line) вместо напряжения питания. Как известно, потребляемая мощность играет важную роль при проектировании сверхбольших интегральных схем (СБИС) и входит в число основных проблем отрасли производства полупроводниковых кристаллов. С целью поддержания эффективности выполнения операции записи получено пониженное значение DRV и увеличено время хранения ячейки eDRAM при помощи разработанной схемы, названной «форсированной усиливающей 3Т ячейкой eDRAM-памяти». Предложенный тип ячейки eDRAM использует RWL шину посредством трех p-канальных MOS транзисторов (PMOS), вместо n-канальных MOS транзисторов (NMOS). PMOS транзисторы являются предпочтительными, поскольку обладают намного меньшим током утечки затвора, что обеспечивает лучшие результаты для удержания данных и увеличивает время хранения ячейки. Результаты проведенного моделирования получены с помощью программного пакета Cadence Virtuoso Tool при использовании 45 нм технологии для предложенной модели. На основании моделирования сделан вывод, что по сравнению с обычной усиливающей ячейкой eDRAM-памяти параметры предложенной ячейки существенно улучшены: статическая мощность составляет 0,767 пВт, напряжение DRV равно 142,009 мВ, шум составляет 8,421 нВ/Гц1/2.

Посилання

- Sze S. M. Physics of Semiconductor Devices / S. M. Sze. — 2nd ed. — New York: Wiley, 1981.

- Matick R. E. Logic-based eDRAM: Origins and rationale for use / R. E. Matick, S. E. Schuster // IBM J. Res. Develop. — Jan. 2005. — Vol. 49, No. 1. — P. 145–165. — DOI : http://dx.doi.org/10.1147/rd.491.0145.

- A 500 MHz random cycle, 1.5 ns latency, SOI embedded DRAM macro featuring a three-transistor micro sense amplifier / J. Barth, W. R. Reohr, P. Parries, G. Fredeman, J. Golz, S. E. Schuster, Richard E. Matick, H. Hunter, C. C. Tanner, J. Harig, H. Kim, B. A. Khan, J. Griesemer, R. P. Havreluk, K. Yanagisawa, T. Kirihata, S. S. Iyer // IEEE J. Solid-State Circuits. — Jan. 2008. — Vol. 43, No. 1. — P. 86–95. — DOI : http://dx.doi.org/10.1109/JSSC.2007.908006.

- Luk W. K. A 3-transistor DRAM cell with gated diode for enhanced speed and retention time / W. K. Luk, Jin Cai, R. H. Dennard, M. J. Immediato, S. V. Kosonocky // Proc. of IEEE Symp. on VLSI Circuits : Honolulu, HI : Digest of Technical Papers. — IEEE, 2006. — P. 184–185. — DOI : http://dx.doi.org/10.1109/VLSIC.2006.1705371.

- Chun K. C. A sub-0.9V logic-compatible embedded DRAM with boosted 3T gain cell, regulated bit-line write scheme and PVT-tracking read reference bias / Ki Chul Chun, P. Jain, Jung Hwa Lee, C. H. Kim // IEEE Symp. VLSI Circuits : 16–18 June 2009, Kyoto, Japan : proc. — IEEE, 2009. — P. 134–135. — URL : http://ieeexplore.ieee.org/xpl/login.jsp?tp=&arnumber=5205419&url=http%3A%2F%2Fieeexplore.ieee.org%2Fxpls%2Fabs_all.jsp%3Farnumber%3D5205419.

- Kiyoo Itoh B. S. Trends in megabit DRAM circuit design / B. S. Kiyoo Itoh // IEEE J. Solid-State Circuits. — Jun. 1990. — Vol. 25, No. 3. — P. 778–789. — DOI : http://dx.doi.org/10.1109/4.102676.

- Akashe S. A low leakage current power 45-nm CMOS SRAM / Shyam Akashe, Deepak Kumar Sinha, Sanjay Sharma // Indian J. Sci. Technol. — 2011. — Vol. 4, No. 4. — P. 440–442. — DOI : http://dx.doi.org/10.17485/ijst/2011/v4i4/30019.

- Shrivastava A. Low power analysis in single stage source coupled VCO with AVL technique using nanoscale CMOS technology / Akansha Shrivastava, Saurabh Khandelwal, Shyam Akashe // Engineering and Systems : IEEE Students Conf. SCES, 12–14 Apr. 2013, Allahabad, India. — IEEE, 2013. — P. 1–6. — DOI : http://dx.doi.org/10.1109/SCES.2013.6547488.

- Chandrakasan A. P. Low Power Digital CMOS Design / A. P. Chandrakasan, R. W. Brodersen. — Wiley–IEEE Press, Jan. 1998.

- Butts J. A. A static power model for architects / J. A. Butts, G. S. Sohi // Microarchitecture : 33rd Annual IEEE/ACM Int. Symp. MICRO-33, 10–13 Dec. 2000, Monterey, CA. — IEEE, 2000. — P. 191–201. — DOI : http://dx.doi.org/10.1109/MICRO.2000.898070.

- Seevinck E. Current-mode techniques for high-speed VLSI circuits with application to current sense amplifier for CMOS SRAM’s / E. Seevinck, P. J. van Beers, H. Ontrop // IEEE J. Solid-State Circuits. — Apr. 1991. — Vol. 26, No. 4. — P. 525–536. — DOI : http://dx.doi.org/10.1109/4.75050.

- A 1.8-V 128-Mb mobile DRAM with double boosting pump, hybrid current sense amplifier, and dual-referenced adjustment scheme for temperature sensor / Jae-Yoon Sim, Hongil Yoon, Ki-Chul Chun, Hyun-Seok Lee, Sang-Pyo Hong, Kyu-Chan Lee, Jei-Hwan Yoo, Dong-Il Seo, Soo-In Cho // IEEE J. Solid-State Circuits. — Apr. 2003. — Vol. 38, No. 4. — P. 631–640. — DOI : http://dx.doi.org/10.1109/JSSC.2003.809514.

##submission.downloads##

Опубліковано

Як цитувати

Номер

Розділ

Ліцензія

Авторське право (c) 2016 Известия высших учебных заведений. РадиоэлектроникаИздатель журнала Известия высших учебных заведений. Радиоэлектроника (сокр. "Известия вузов. Радиоэлектроника"), Национальный технический университет Украины "Киевский политехнический институт", учитывает, что доступ автора к его статье является важным как для самого автора, так и для спонсоров его исследований. Мы представлены в базе издателей SHERPA/RoMEO как зеленый издатель (green publisher), что позволяет автору выполнять самоархивирование своей статьи. Однако важно, чтобы каждая из сторон четко понимала свои права. Просьба более детально ознакомиться с Политикой самоархивирования нашего журнала.

Политика оплаченного открытого доступа POA (paid open access), принятая в журнале, позволяет автору выполнить все необходимые требования по открытому доступу к своей статье, которые выдвигаются институтом, правительством или фондом при выделении финансирования. Просьба более детально ознакомиться с политикой оплаченного открытого доступа нашего журнала (см. отдельно).

Варианты доступа к статье:

1. Статья в открытом доступе POA (paid open access)

В этом случае права автора определяются лицензией CC BY (Creative Commons Attribution).

2. Статья с последующим доступом по подписке

В этом случае права автора определяются авторским договором, приведенным далее.

- Автор (каждый соавтор) уступает Издателю журнала «Известия высших учебных заведений. Радиоэлектроника» НТУУ «КПИ» на срок действия авторского права эксклюзивные права на материалы статьи, в том числе право на публикацию данной статьи издательством Аллертон Пресс, США (Allerton Press) на английском языке в журнале «Radioelectronics and Communications Systems». Передача авторского права охватывает исключительное право на воспроизведение и распространение статьи, включая оттиски, переводы, фото воспроизведения, микроформы, электронные формы (он- и оффлайн), или любые иные подобные формы воспроизведения, а также право издателя на сублицензирование третьим лицам по своему усмотрению без дополнительных консультаций с автором. При этом журнал придерживается Политики конфиденциальности.

- Передача прав включает право на обработку формы представления материалов с помощью компьютерных программам и систем (баз данных) для их использования и воспроизводства, публикации и распространения в электронном формате и внедрения в системы поиска (базы данных).

- Воспроизведение, размещение, передача или иное распространение или использование материалов, содержащихся в статье должно сопровождаться ссылкой на Журнал и упоминанием Издателя, а именно: название статьи, имя автора (соавторов), название журнала, номер тома, номер выпуска, копирайт авторов и издателя "© Национальный технический университет Украины "Киевский политехнический институт"; © автор(ы)".

- Автор (каждый соавтор) материалов сохраняет все права собственника материалов, включая патентные права на любые процессы, способы или методы и др., а также права на товарные знаки.

- Издатель разрешает автору (каждому соавтору) материалов следующее:

- Право пользоваться печатными или электронными вариантами материалов статьи в форме и содержании, принятыми Издателем для публикации в Журнале. Подробнее см. политики Оплаченного открытого доступа, подписки и самоархивирования.

- Право бесплатно копировать или передавать коллегам копию напечатанной статьи целиком или частично для их личного или профессионального использования, для продвижения академических или научных исследований или для учебного процесса или других информационных целей, не связанных с коммерческими целями.

- Право использовать материалы из опубликованной статьи в написанной автором (соавторами) книге, монографии, учебнике, учебном пособии и других научных и научно-популярных изданиях.

- Право использовать отдельные рисунки или таблицы и отрывки текста из материалов в собственных целях обучения или для включения их в другую работу, которая печатается (в печатном или электронном формате) третьей стороной, или для представления в электронном формате во внутренние компьютерные сети или на внешние сайты автора (соавторов).

- Автор (соавторы) соглашаются, что каждая копия материалов или любая ее часть, распространенная или размещенная ими в печатном или электронном формате, будет содержать указание на авторское право, предусмотренное в Журнале и полную ссылку на Журнал Издателя.

- Автор (соавторы) гарантирует, что материалы являются оригинальной работой и представлены впервые на рассмотрение только в этом Журнале и ранее не публиковались. Если материалы написаны совместно с соавторами, автор гарантирует, что проинформировал их относительно условий публикации материалов и получил их подписи или письменное разрешение подписываться от их имени.

- Если в материалы включаются отрывки из работ или имеются указания на работы, которые охраняются авторским правом и принадлежат третьей стороне, то автору необходимо получить разрешение владельца авторских прав на использование таких материалов в первом случае и сделать ссылку на первоисточник во втором.

- Автор гарантирует, что материалы не содержат клеветнических высказываний и не посягают на права (включая без ограничений авторское право, права на патент или торговую марку) других лиц и не содержат материалы или инструкции, которые могут причинить вред или ущерб третьим лицам. Автор (каждый соавтор) гарантирует, что их публикация не приведет к разглашению секретных или конфиденциальных сведений (включая государственную тайну). Подтверждением этого является Экспертное заключение (см. перечень документов в Правила для авторов).

- Издатель обязуется опубликовать материалы в случае получения статьей положительного решения редколлегии о публикации на основании внешнего рецензирования (см. Политика рецензирования).

- В случае публикации статьи на английском языке в журнале «Radioelectronics and Communications Systems» (Издатель: Аллертон Пресс, США, распространитель Springer) автору (соавторам) выплачивается гонорар после выхода последнего номера журнала года, в котором опубликована данная статья.

- Документ Согласие на публикацию, который подают русскоязычные авторы при подаче статьи в редакцию, является краткой формой данного договора, в котором изложены все ключевые моменты настоящего договора и наличие которого подтверждает согласие автора (соавторов) с ним. Аналогичным документом для англоязычных авторов является Copyright Transfer Agreement (CTA), предоставляемый издательством Allerton Press.

- Настоящий Договор вступает в силу в момент принятия статьи к публикации. Если материалы не принимаются к публикации или до публикации в журнале автор (авторы) отозвал работу, настоящий Договор не приобретает (теряет) силу.