Кольцевой генератор с цифровым управлением и широким диапазоном перестройки

DOI:

https://doi.org/10.20535/S0021347020020016Ключові слова:

кольцевой генератор с цифровым управлением, DRO, широкий диапазон частот, высокая частотаАнотація

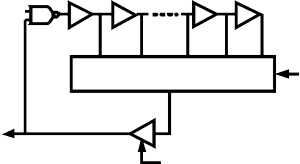

В статье предложены два кольцевых генератора с цифровым управлением DRO (digitally-controlled ring oscillator), имеющих сходную структуру, но различные конструктивные ячейки. Предлагаемые DRO состоят из 5 каскадов, причем каждый каскад содержит 10 параллельных элементов задержки. Кроме того, каждый каскад содержит две части для точной и грубой подстройки выходной частоты. Предлагаемые конструкции обладают широким частотным диапазоном и генерируют сигнал высокой частоты. Частотный диапазон первого DRO изменяется от 1,566 до 20,25 ГГц (92,6%), а частотный диапазон второго DRO изменяется от 2,218 до 22,86 ГГц (90,31%). Если рассматривать все возможные цифровые коды для каскадов точной и грубой подстройки, потребляемая мощность первого DRO изменяется от 1,1 до 13,64 мВт, тогда как мощность второго DRO изменяется от 144,1 мкВт до 1,76 мВт. Фазовый шум первого DRO при центральной частоте 20,25 ГГц и сдвиге частоты 1 МГц составляет –76,24 дБн/Гц, а при сдвиге частоты 10 МГц, указанный фазовый шум составляет –104 дБн/Гц. Фазовый шум второго DRO при центральной частоте 22,86 ГГц и сдвиге частоты 1 МГц составляет –66,64 дБн/Гц, а при сдвиге частоты 10 МГц, указанный фазовый шум составляет –95,39 дБн/Гц. В этой работе осуществлялось моделирование предлагаемых генераторов в программном пакете Cadence при использовании 65нм CMOS технологии компании TSMC и напряжении питания 1,2 В.Посилання

- M. L. Sheu, Y. S. Tiao, and L. J. Taso, “A 1-V 4-GHz wide tuning range voltage-controlled ring oscillator in 0.18 μm CMOS,” Microelectronics J., vol. 42, no. 6, pp. 897–902, Jun. 2011, doi: https://doi.org/10.1016/j.mejo.2011.03.015.

- C. C. Chung, C. Y. Ko, and S. E. Shen, “Built-in self-calibration circuit for monotonic digitally controlled oscillator design in 65-nm CMOS technology,” IEEE Trans. Circuits Syst. II Express Briefs, vol. 58, no. 3, pp. 149–153, Mar. 2011, doi: https://doi.org/10.1109/TCSII.2011.2110370.

- C. C. Chung and C. Y. Ko, “A Fast phase tracking ADPLL for video pixel clock generation in 65 nm CMOS technology,” IEEE J. Solid-State Circuits, vol. 46, no. 10, pp. 2300–2311, Oct. 2011, doi: https://doi.org/10.1109/JSSC.2011.2160789.

- Y. P. Chen et al., “Persistent Laser-Induced Leakage in a 20 nm Charge-Pump Phase-Locked Loop (PLL),” IEEE Trans. Nucl. Sci., vol. 64, no. 1, pp. 512–518, Jan. 2017, doi: https://doi.org/10.1109/TNS.2016.2627940.

- J. M. Lin and C. Y. Yang, “A fast-locking all-digital phase-locked loop with dynamic loop bandwidth adjustment,” IEEE Trans. Circuits Syst. I Regul. Pap., vol. 62, no. 10, pp. 2411–2422, Oct. 2015, doi: https://doi.org/10.1109/TCSI.2015.2477575.

- R. Khalirbaginov and A. Haymin, “Novel HDL design of digital controlled oscillator for ADPLL,” in Proceedings of the 2019 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering, ElConRus 2019, 2019, pp. 1678–1682, doi: https://doi.org/10.1109/EIConRus.2019.8657238.

- H. Yoon, S. Park, and J. Choi, “A Low-Jitter Injection-Locked Multi-Frequency Generator Using Digitally Controlled Oscillators and Time-Interleaved Calibration,” IEEE J. Solid-State Circuits, vol. 54, no. 6, pp. 1564–1574, Jun. 2019, doi: https://doi.org/10.1109/JSSC.2019.2893513.

- C. H. Wong, Y. Li, J. Du, X. Wang, and M. C. F. Chang, “0.75 V 2.6 GHz digital bang–bang PLL with dynamic double-tail phase detector and supply-noise-tolerant gm-controlled DCO,” Electron. Lett., vol. 54, no. 4, pp. 198–200, Feb. 2018, doi: https://doi.org/10.1049/el.2017.4168.

- C. M. Lin, K. Y. Kao, and K. Y. Lin, “A wideband, low-noise, and high-resolution digitally-controlled oscillator for SDR applications,” in Asia-Pacific Microwave Conference Proceedings, APMC, 2019, vol. 2018-Novem, pp. 270–272, doi: https://doi.org/10.23919/APMC.2018.8617605.

- L. Xiu, X. Wei, and Y. Ma, “A full digital fractional-N TAF-FLL for digital applications: Demonstration of the principle of a frequency-locked loop built on time-average-frequency,” IEEE Trans. Very Large Scale Integr. Syst., vol. 27, no. 3, pp. 524–534, Mar. 2019, doi: https://doi.org/10.1109/TVLSI.2018.2888625.

- C. C. Chung, D. Sheng, and C. H. Chen, “An all-digital phase-locked loop compiler with liberty timing files,” in Technical Papers of 2014 International Symposium on VLSI Design, Automation and Test, VLSI-DAT 2014, 2014, doi: https://doi.org/10.1109/VLSI-DAT.2014.6834903.

- T. Siriburanon et al., “A 2.2 GHz-242 dB-FOM 4.2 mW ADC-PLL Using Digital Sub-Sampling Architecture,” IEEE J. Solid-State Circuits, vol. 51, no. 6, pp. 1385–1397, Jun. 2016, doi: https://doi.org/10.1109/JSSC.2016.2546304.

- P. Muppala, “High-frequency Wide-Range All Digital Phase Locked Loop in 90nm CMOS,” Brows. all Theses Diss., Jan. 2011, Accessed: 01-Mar-2020. [Online]. Available: https://corescholar.libraries.wright.edu/etd_all/1056.

- J. A. F. da Cruz, “A Study on Digitally Controlle Oscillators for All-Digital Phase-Locked Loops,” FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO A, 2015.

- Амритакар Мандал, Раджеш Мишра, М. Р. Нагар, “Реализация комплексной цифровой системы ФАПЧ для фазового детектирования в программно определяемом радаре,” Известия вузов. Радиоэлектроника, Т. 59, № 4, С. 3–18, 2016. DOI: https://doi.org/10.20535/S0021347016040014.

- A. Ramazani, S. Biabani, and G. Hadidi, “CMOS ring oscillator with combined delay stages,” AEU - Int. J. Electron. Commun., vol. 68, no. 6, pp. 515–519, Jun. 2014, doi: https://doi.org/10.1016/j.aeue.2013.12.008.

- C. T. Jung and Y. Ho, “Design of a temperature-insensitive digitally-controlled oscillator for on-chip reference clock,” in Proceedings - 2018 IEEE International Conference on Industrial Electronics for Sustainable Energy Systems, IESES 2018, 2018, vol. 2018-Janua, pp. 499–503, doi: https://doi.org/10.1109/IESES.2018.8349928.

- T. Lee, Y. H. Kim, and L. S. Kim, “A 5-Gb/s digital clock and data recovery circuit with reduced DCO supply noise sensitivity utilizing coupling network,” IEEE Trans. Very Large Scale Integr. Syst., vol. 25, no. 1, pp. 380–384, Jan. 2017, doi: https://doi.org/10.1109/TVLSI.2016.2566927.

- S. Salem, M. Tajabadi, and M. Saneei, “The design and analysis of dual control voltages delay cell for low power and wide tuning range ring oscillators in 65 nm CMOS technology for CDR applications,” AEU - Int. J. Electron. Commun., vol. 82, pp. 406–412, Dec. 2017, doi: https://doi.org/10.1016/j.aeue.2017.10.012.

- W. T. Lee, J. Shim, and J. Jeong, “Design of a three-stage ring-type voltage-controlled oscillator with a wide tuning range by controlling the current level in an embedded delay cell,” Microelectronics J., vol. 44, no. 12, pp. 1328–1335, Dec. 2013, doi: https://doi.org/10.1016/j.mejo.2013.09.003.

- Z. Z. Chen, Y. C. Kuan, Y. Li, B. Hu, C. H. Wong, and M. C. F. Chang, “DPLL for Phase Noise Cancellation in Ring Oscillator-Based Quadrature Receivers,” IEEE J. Solid-State Circuits, vol. 52, no. 4, pp. 1134–1143, Apr. 2017, doi: https://doi.org/10.1109/JSSC.2017.2647925.

- J. Gorji and M. B. Ghaznavi-Ghoushchi, “A 2.7 to 4.6 GHz multi-phase high resolution and wide tuning range digitally-controlled oscillator in CMOS 65nm,” in 2016 24th Iranian Conference on Electrical Engineering, ICEE 2016, 2016, pp. 1694–1699, doi: https://doi.org/10.1109/IranianCEE.2016.7585794.

- M. E. S. Elrabaa, “A portable high-frequency digitally controlled oscillator (DCO),” Integr. VLSI J., vol. 47, no. 3, pp. 339–346, Jun. 2014, doi: https://doi.org/10.1016/j.vlsi.2013.10.009.

- M. Kumar, S. K. Arya, and S. Pandey, “Digitally controlled oscillator design with a variable capacitance XOR gate,” J. Semicond., vol. 32, no. 10, p. 105001, 2011, doi: https://doi.org/10.1088/1674-4926/32/10/105001.

- M. C. Su, S. J. Jou, and W. Z. Chen, “A Low-Jitter Cell-Based Digitally Controlled Oscillator With Differential Multiphase Outputs,” IEEE Trans. Very Large Scale Integr. Syst., vol. 23, no. 4, pp. 766–770, Apr. 2015, doi: https://doi.org/10.1109/TVLSI.2014.2314740.

- D. Sheng, C. C. Chung, and C. Y. Lee, “An ultra-low-power and portable digitally controlled oscillator for SoC applications,” IEEE Trans. Circuits Syst. II Express Briefs, vol. 54, no. 11, pp. 954–958, 2007, doi: https://doi.org/10.1109/TCSII.2007.903782.

- P. Muppala, S. Ren, and G. Y. H. Lee, “Design of high-frequency wide-range all digital phase locked loop in 90 nm CMOS,” Analog Integr. Circuits Signal Process., vol. 75, no. 1, pp. 133–145, Apr. 2013, doi: https://doi.org/10.1007/s10470-013-0043-9.

- D. De Caro, “Glitch-free NAND-based digitally controlled delay-lines,” IEEE Trans. Very Large Scale Integr. Syst., vol. 21, no. 1, pp. 55–66, 2013, doi: https://doi.org/10.1109/TVLSI.2011.2181547.

- K. H. Choi, J. B. Shin, J. Y. Sim, and H. J. Park, “An interpolating digitally controlled oscillator for a wide-range all-digital PLL,” IEEE Trans. Circuits Syst. I Regul. Pap., vol. 56, no. 9, pp. 2055–2063, 2009, doi: https://doi.org/10.1109/TCSI.2008.2011577.

- A. Abadian, M. Lotfizad, M. B. Ghaznavi-Ghoushchi, and N. E. Majd, “An ultra low power and low complexity all digital PLL with a high resolution digitally controlled oscillator,” IEICE Electron. Express, vol. 8, no. 21, pp. 1801–1807, Nov. 2011, doi: https://doi.org/10.1587/elex.8.1801.

- R. K. Pokharel et al., “Digitally controlled ring oscillator using fraction-based series optimization for inductorless reconfigurable all-digital PLL,” in 2011 IEEE 11th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, SiRF 2011 - Digest of Papers, 2011, pp. 69–72, doi: https://doi.org/10.1109/SIRF.2011.5719321.

- E. R. Suraparaju, P. V. R. Arja, and S. Ren, “A 1.1-8.2 GHz tuning range In-phase and Quadrature output DCO design in 90 nm CMOS technology,” in Midwest Symposium on Circuits and Systems, 2015, vol. 2015-September, doi: https://doi.org/10.1109/MWSCAS.2015.7282171.

- J. M. Rabaey, Digital Integrated Circuits: A Design Perspective, 2nd ed. PH, 2003.

##submission.downloads##

Опубліковано

2020-02-21

Як цитувати

Аскари, Ш., & Саней, М. (2020). Кольцевой генератор с цифровым управлением и широким диапазоном перестройки. Вісті вищих учбових закладів. Радіоелектроніка, 63(2), 71–82. https://doi.org/10.20535/S0021347020020016

Номер

Розділ

Оригінальні статті