Дослідження режимів вихідної генерації лінеаризованих штучних нейронів на базі апаратного рішення із ПЛІС архітектурою

DOI:

https://doi.org/10.20535/S0021347020020053Ключові слова:

модель штучного нейрона, математична модель нейрону, штучна нейронна мережа, мультистабільна нейронна мережа, ПЛІС, Spartan-3E, VHDLАнотація

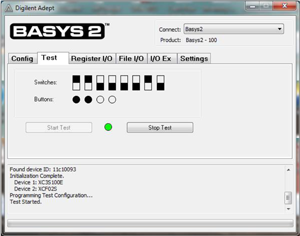

Виконано розробку вбудованого програмного забезпечення для впровадження та тестування базової поведінки штучної моделі мультистабільного нейрона за допомогою апаратної архітектури програмованих логічних інтегральних схем (ПЛІС). Досліджено і реалізовано реальну поведінку і функцію біологічного нейрона із лінеаризованими характеристиками активації мовою програмування VHDL. За базову обрано модель тристабільного нейрона з трьома асиметричними дендритами. Для розробки апаратної моделі використано компартментальну математичну модель нейрона, на базі якої синтезовано відповідну дискретну модель. Модель складається з таких модулів як вхідний блок, таймер, генератор тактової частоти, пороговий елемент та блок генерації вихідного сигналу. Показано, що реалізована система дозволяє синтезувати нейронну модель із заздалегідь заданим числом стабільних дискретних станів, при цьому нейрон зміню свій стабільний стан в залежності від вхідного вектору. Кожному стабільному стану відповідає своя вихідна функція нейрона. Розроблена модель штучних нейронів реалізована на комплектації Digilent Basys ІІ Spartan-3E XC3S100E FPGA у середовищі WebPACKTM ISE 13.3. Наведено результати генерації різних вихідних паттернів, в залежності від послідовності вхідних синаптичних активацій та структури нейрона. Результати роботи дозволяють дослідити швидкодіючі нейронні мережі із динамічною структурою із застосуванням ПЛІС, що може бути використано для широкого кола сучасних задач, таких як розпізнавання, класифікація паттернів і для розробки елементів штучного інтелекту.Посилання

- J. A. Bailey, R. Wilcock, P. R. Wilson, and J. E. Chad, “Behavioral simulation and synthesis of biological neuron systems using synthesizable VHDL,” Neurocomputing, vol. 74, no. 14–15, pp. 2392–2406, Jul. 2011, doi: https://doi.org/10.1016/j.neucom.2011.04.001.

- P. Wilson, B. Metcalfe, J. Graham-Harper-Cater, and J. A. Bailey, “A reconfigurable architecture for real-time digital simulation of neurons,” in 2017 Intelligent Systems Conference, IntelliSys 2017, 2018, vol. 2018-January, pp. 66–75, doi: https://doi.org/10.1109/IntelliSys.2017.8324340.

- R. R. Borges et al., “Effects of the spiketiming-dependent plasticity on the synchronisation in a random Hodgkin-Huxley neuronal network,” Commun. Nonlinear Sci. Numer. Simul., vol. 34, pp. 12–22, 2016, doi: https://doi.org/10.1016/j.cnsns.2015.10.005.

- J. E. G-H-Cater, C. T. Clarke, B. W. Metcalfe, and P. R. Wilson, “A reconfigurable architecture for implementing locally connected neural arrays,” in Advances in Intelligent Systems and Computing, 2019, vol. 857, pp. 76–92, doi: https://doi.org/10.1007/978-3-030-01177-2_6.

- I. Sahin and N. K. Saritekin, “A data path design tool for automatically mapping artificial neural networks on to FPGA-based systems,” J. Electr. Eng. Technol., vol. 11, no. 5, pp. 1466–1474, Sep. 2016, doi: https://doi.org/10.5370/JEET.2016.11.5.1466.

- E. Z. Mohammed and H. K. Ali, “Hardware Implementation of Artificial Neural Network Using Field Programmable Gate Array,” Int. J. Comput. Theory Eng., pp. 780–783, 2013, doi: https://doi.org/10.7763/ijcte.2013.v5.795.

- F. Pérez-Peña, A. Morgado-Estévez, and A. Linares-Barranco, “Inter-spikes-intervals exponential and gamma distributions study of neuron firing rate for SVITE motor control model on FPGA,” Neurocomputing, vol. 149, no. PB, pp. 496–504, Feb. 2015, doi: https://doi.org/10.1016/j.neucom.2014.08.024.

- F. Akopyan et al., “TrueNorth: Design and Tool Flow of a 65 mW 1 Million Neuron Programmable Neurosynaptic Chip,” IEEE Trans. Comput. Des. Integr. Circuits Syst., vol. 34, no. 10, pp. 1537–1557, Oct. 2015, doi: https://doi.org/10.1109/TCAD.2015.2474396.

- W. Rawat and Z. Wang, “Deep convolutional neural networks for image classification: A comprehensive review,” Neural Computation, vol. 29, no. 9. MIT Press Journals, pp. 2352–2449, 01-Sep-2017, doi: https://doi.org/10.1162/NECO_a_00990.

- Y. Ghelamallah, D. Chalabi, A. Saïdane, and Z. Chalabi, “Implementation on FPGA circuit of the medical image processing algorithms within the framework of assistance to the medical diagnosis,” Int. Rev. Comput. Softw., vol. 10, no. 10, pp. 987–994, 2015, doi: https://doi.org/10.15866/irecos.v10i10.7155.

- A. Podili, C. Zhang, and V. Prasanna, “Fast and efficient implementation of Convolutional Neural Networks on FPGA,” in Proceedings of the International Conference on Application-Specific Systems, Architectures and Processors, 2017, pp. 11–18, doi: https://doi.org/10.1109/ASAP.2017.7995253.

- S. M. Korogod and D. V. Chernetchenko, “Nature of Electrical Tristability in a Neuron Model with Bistable Asymmetrical Dendrites,” Neurophysiology, vol. 40, no. 5–6, pp. 412–416, Sep. 2008, doi: https://doi.org/10.1007/s11062-009-9067-2.

- Є. М. Сніжко і Д. В. Чернетченко, “Динаміка електричних потенціалів моделі мережі нейронів із нелінійними функціями активації,” Вісник ДНУ. Серія Фізика. Радіоелектроніка, Т. 20, № 2, с. 50–57, 2012.

- A. Alaburda, M. Alaburda, A. Baginskas, A. Gutman, and G. Svirskis, “Criteria of bistability of the cylindrical dendrite with a variable negative slope of the N-shaped current-voltage membrane characteristic,” Biofizika, vol. 46, no. 2, p. 340, 2001, Accessed: 04-Feb-2020. [Online]. Available: http://www.ncbi.nlm.nih.gov/pubmed/11368033.

- S. Yin et al., “A High Energy Efficient Reconfigurable Hybrid Neural Network Processor for Deep Learning Applications,” IEEE J. Solid-State Circuits, vol. 53, no. 4, pp. 968–982, Apr. 2018, doi: https://doi.org/10.1109/JSSC.2017.2778281.

##submission.downloads##

Опубліковано

2020-03-28

Як цитувати

Сніжко, Є. М., & Чернетченко, Д. В. (2020). Дослідження режимів вихідної генерації лінеаризованих штучних нейронів на базі апаратного рішення із ПЛІС архітектурою. Вісті вищих учбових закладів. Радіоелектроніка, 63(2), 114–124. https://doi.org/10.20535/S0021347020020053

Номер

Розділ

Оригінальні статті