Экономное моделирование и реализация генератора тестовых сигналов для определения характеристик сигма-дельта АЦП в непрерывном времени

DOI:

https://doi.org/10.20535/S0021347019050066Ключові слова:

вычисление гистограммы, сигма-дельта модулятор, генератор управляющего воздействия, TSG, CORDIC, BIST, ORA, SDMАнотація

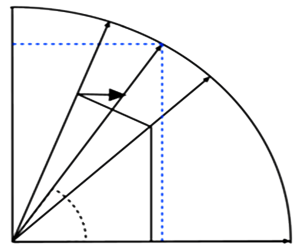

В настоящее время существует огромное количество различных приложений, связанных с беспроводной связью, что выдвигает специфические требования к микросхемам обработки смешанных сигналов. Когда эти независимые схемы применяются в конструкции АЦП и ЦАП, значительно возрастает сложность тестирования. Для уменьшения этой сложности традиционно используется BIST-технология, которая предотвращает функциональную зависимость от дорогого тестового оборудования АТЕ. Кроме того, в системе встроенного самотестирования BIST (Built-In-self-Test) анализатор выходного отклика ORA (Output Response Analyzer) является наиболее важным элементом архитектуры сигма-дельта аналогово-цифрового преобразователя (АЦП) в непрерывном времени CT (continuous time). Существует множество алгоритмов ORA для точного определения параметров конструкции, таких как интегральная нелинейность INL (integral non-linearity), дифференциальная нелинейность DNL (differential non-linearity) и отношение сигнал–шум SNR (signal-to-noise ratio). В данной работе используется современный метод CORDIC, который используется в качестве ORA. Для точного имитационного моделирования этого метода использованы программные компоненты Matlab simulink и CADENCE VIRTUOSO EDA. Показано, что метод цифрового вычислителя поворота системы координат CORDIC (Coordinate Rotation Digital Computer) использован для уменьшения сложности конструкции независимых схем. Конструкция АЦП также может быть значительно улучшена с помощью BIST. В данной работе рассмотрено на системном уровне моделирование тестового генератора управляющего воздействия TSG (test stimuli generator) и его моделирование для точного определения сигналов сигма-дельта АЦП высокого разрешения. Успешная реализация протестирована в среде Matlab simulink. Автоматическая проверка аппаратуры внешнего тестирования необходима для испытания интегрированных структур. Реализованный TSG помогает вычислить статистику и параметры передачи, требуемые для получения характеристик СТ сигма-дельта АЦП.Посилання

- Lin, C.-H.; Wu, A.-Y. “Mixed-scaling-rotation CORDIC (MSR-CORDIC) algorithm and architecture for high-performance vector rotational DSP applications,” IEEE Trans. Circuits Systems I: Regular Papers, Vol. 52, No. 11, p. 2385-2396, 2005. DOI: https://doi.org/10.1109/TCSI.2005.853908.

- Maharatna, K.; El-Shabrawy, K.; Al-Hashimi, B. “Reduced Z-datapath CORDIC rotator,” Proc. of IEEE Int. Symp. on Circuits and Systems, 18-21 May 2008, Seattle, USA. IEEE, 2008, p. 3374-3377. DOI: https://doi.org/10.1109/ISCAS.2008.4542182.

- Hu, Y. H. “The quantization effects of the CORDIC algorithm (coordinate rotation digital computer),” Proc. of Int. Conf. on Acoustics, Speech, and Signal Processing, 11-14 1988, NewYork, USA. IEEE, 1988, p. 1822-1825. DOI: https://doi.org/10.1109/ICASSP.1988.196976.

- Peng, C.-S.; Chuang, Y.-S.; Wen, K.-A. “CORDIC-based architecture with channel state information for OFDM baseband receiver,” IEEE Trans. Consumer Electronics, Vol. 51, No. 2, p. 403-412, 2005. DOI: https://doi.org/10.1109/TCE.2005.1467979.

- Kar, D. C.; Rao, V. V. B. “A CORDIC-based unified systolic architecture for sliding window applications of discrete transforms,” IEEE Trans. Signal Processing, Vol. 44, No. 2, p. 441-444, 1996. DOI: https://doi.org/10.1109/78.485943.

- De Souza, C. P.; de Assis, F. M.; Freire, R. C. S. “A new architecture of test response analyzer based on the Berlekamp-Massey algorithm for BIST,” IEEE Trans. Instrum. Meas., Vol. 59, No. 12, p. 3168-3173, 2010. DOI: https://doi.org/10.1109/TIM.2010.2047171.

- Ting, H.-W.; Chao, I.-J.; Lien, Y.-C.; Chang, S.-J.; Liu, B.-D. “A low-cost output response analyzer circuit for ADC BIST,” Proc. of IEEE Circuits and Systems Int. Conf. on Testing and Diagnosis, 28-29 Apr. 2009, Chengdu, China. IEEE, 2009, p. 1-4. DOI: https://doi.org/10.1109/CAS-ICTD.2009.4960751.

- De Souza, C. P.; de Assis, F. M.; Freire, R. C. S. “Circuit testing using the principles of self-nonself discrimination,” IEEE Trans. Instrum. Meas., Vol. 57, No. 9, p. 1978-1983, 2008. DOI: https://doi.org/10.1109/TIM.2008.919002.

- Kim, H.; Lee, K.-S. “Sigma-delta ADC characterization using noise transfer function pole-zero tracking,” Proc. of IEEE Int. Test Conf., 21-26 Oct. 2006, Santa Clara, USA. IEEE, 2006, p. 1-9. DOI: https://doi.org/10.1109/TEST.2007.4437654.

- Arpaia, P.; Cennamo, F.; Daponte, P.; Schumny, H. “Modeling and characterization of sigma-delta analog-to-digital converters,” IEEE Trans. Instrum. Meas., Vol. 52, No. 3, p. 978-983, 2003. DOI: https://doi.org/10.1109/TIM.2003.809106.

- Michaeli, L.; Saliga, J. “Error models of the analog to digital converters,” Meas. Sci. Rev., Vol. 14, No. 2, p. 62-77, 2014. DOI: https://doi.org/10.2478/msr-2014-0010.

- Parkey, C. R.; Chester, D. B.; Hunter, M. T.; Mikhael, W. B. “Simulink modeling of analog to digital converters for post conversion correction development and evaluation,” Proc. of IEEE 54th Int. Midwest Symp. on Circuits and Systems, MWSCAS, 7-10 Aug. 2010, Seoul, South Korea. IEEE, 2010, p. 1-4. DOI: https://doi.org/10.1109/MWSCAS.2011.6026634.

- Schreier, R.; Pavan, S.; Temes, G. C. “Circuit design for discrete-time delta-sigma ADCs,” in: Understanding Delta-Sigma Data Converters. Wiley-IEEE Press, 2017, p. 584-590. DOI: https://doi.org/10.1002/9781119258308.ch7.

- Chen, T.; Chen, D. “Ultrafast stimulus error removal algorithm for ADC linearity test,” Proc. of IEEE 33rd VLSI Test Symp., VTS, 27-29 Apr. 2015, Napa, USA. IEEE, 2015, p. 1-5. DOI: https://doi.org/10.1109/VTS.2015.7116249.

- Aymerich, J.; Dei, M.; Terés, L.; Serra-Graells, F. “Design of a low-power potentiostatic second-order CT delta-sigma ADC for electrochemical sensors,” Proc. of 13th Conf. on Ph.D. Research in Microelectronics and Electronics, PRIME, 12-15 Jun. 2017, Giardini Naxos, Italy. IEEE, 2017, p. 105-108. DOI: https://doi.org/10.1109/PRIME.2017.7974118.

- El-Rachini, A.; Chible, H.; Nicola, G.; Barbaro, M.; Raffo, L. “Behavioural models for analog to digital conversion architectures for deep submicron technology nodes,” Proc. of 25th Int. Conf. on Microelectronics, ICM, 15-18 Dec. 2013, Beirut, Lebanon. IEEE, 2013, p. 1-4. DOI: https://doi.org/10.1109/ICM.2013.6734973.

- Sahoo, B.; Saxena, V.; Bhatia, K. S. “Tutorial 4B: ADC design - from system architecture to transistor level design,” Proc. of 29th IEEE Int. System-on-Chip Conf., SOCC, 6-9 Sept. 2016, Seattle, USA. IEEE, 2016, p. 1-4. DOI: https://doi.org/10.1109/SOCC.2016.7905414.

- Tripathi, A. K.; Singhal, R.; Verma, A. “Analysis of the system level design of a 1.5 bit/stage pipeline ADC,” Proc. of Fourth Int. Conf. on Advanced Computing & Communication Technologies, 8-9 Feb. 2014, Rohtak, India. IEEE, 2014, p. 89-94. DOI: https://doi.org/10.1109/ACCT.2014.96.

- Marker-Villumsen, N.; Jorgensen, I. H. H.; Bruun, E. “Low power continuous-time delta-sigma ADC with current output DAC,” Proc. of 2015 European Conf. on Circuit Theory and Design, ECCTD, 24-26 Aug. 2015, Trondheim, Norway. IEEE, 2015, p. 1-4. DOI: https://doi.org/10.1109/ECCTD.2015.7300096.

- Vardhini, P. A. H. “Analysis of integrator for continuous time digital sigma delta ADC on Xilinx FPGA,” Proc. of Int. Conf. on Electrical, Electronics, and Optimization Techniques, ICEEOT, 3-5 Mar. 2016, Chennai, India. IEEE, 2016. DOI: https://doi.org/10.1109/ICEEOT.2016.7755184.

- Volder, J. E. “Binary computation algorithms for coordinate rotation and function generation,” Convair Report, IAR-1 148, Aeroelectronics Group, June 1956.

##submission.downloads##

Опубліковано

2019-05-30

Як цитувати

Саху, А. К., Чандра, В. К., & Синха, Г. Р. (2019). Экономное моделирование и реализация генератора тестовых сигналов для определения характеристик сигма-дельта АЦП в непрерывном времени. Вісті вищих учбових закладів. Радіоелектроніка, 62(5), 297–308. https://doi.org/10.20535/S0021347019050066

Номер

Розділ

Оригінальні статті