Выходной буфер 1,8 В на основе 180 нм КМОП технологии для устройств 3,3 В

DOI:

https://doi.org/10.20535/S0021347017110061Ключові слова:

буфер, конвертер уровня, размах напряжения, задержка распространения, падение напряжения, интерфейс PCI-XАнотація

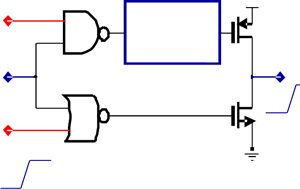

В работе представлен выходной буфер на базе низковольтных устройств (+1,8 В) для работы с сигналами высокого напряжения +3,3 В интерфейса PCI-X (peripheral component interconnect extended), реализованный с помощью КМОП-технологического процесса 180 нм. Поскольку PCI-X является интерфейсом +3,3 В, нагрузка на оксидный затвор создает проблемы при разработке входных-выходных цепей для устройств 180 нм КМОП-процесса. Производительность предложенного выходного буфера оценивалась с применением программы Cadence и параметров модели 180 нм КМОП-процесса. Экспериментальные результаты подтверждают, что предложенный буфер эффективно работает с интерфейсом +3,3 В на частоте 100 МГц без существенного перенапряжения на оксидном затворе. В данной работе также представлен новый преобразователь уровня, реализованный на устройствах +1,8 В, который может преобразовывать размах напряжения 0/1 В в размах напряжения 0/3,3 В. Результаты компьютерного моделирования подтверждают, что предложенный преобразователь работает с достаточной точностью без какого-либо перепада напряжения. Предложенная топология имеет низкую чувствительность, что позволяет ее реализовать на СБИС. Предложенные схемы возможно реализовать с помощью низковольтных устройств без потери производительности.Посилання

- Lin, Yingyan; Zou, Xuecheng; Zheng, Zhaoxiao; Huo, Wenjie; Chen, Xiaofei; Kang, Wenjing. High-speed, low switching noise and load adaptive output buffer. Proc. of IEEE Int. Symp. on Integrated Circuits, ISIC, 14-16 Dec, 2009, Singapore. IEEE, 2009, p.280-282. URI: http://ieeexplore.ieee.org/document/5403888/.

- Scott, R. S.; Dumin, N. A.; Hughes, T. W.; Dumin, D. J.; Moore, B. T. Properties of high-voltage stress generated traps in thin silicon oxide. IEEE Trans. Electron Devices, v.43, n.7, p.1133-1143, 1996. DOI: https://doi.org/10.1109/16.502425.

- Mahendranath, B.; Srinivasulu, A. Analysis of two new voltage level converters with various load conditions. Int. J. Advances Telecommunications, Electrotechnics, Signals and Systems, v.2, n.3, p.92-98, 2013. URI: http://www.ijates.org/index.php/ijates/article/view/45.

- Srinivasulu, A.; Rajesh, M. ULPD and CPTL pull-up stages for differential cascode voltage switch logic. J. Engineering, v.2013, Article ID 595296, 5 pages, 2013. DOI: http://dx.doi.org/10.1155/2013/595296.

- Sundari, A. B. T.; Srinivasulu, Avireni. High speed level converters with short circuit current reduction. Int. J. Advances in Telecommunications, Electrotechnics, Signals and Systems, v.3, n.2, p.44-52, 2014. DOI: http://dx.doi.org/10.11601/ijates.v3i2.92.

- Mahendranath, B.; Srinivasulu, Avireni. Performance analysis of a new CMOS output buffer. Proc. of IEEE Int. Conf. on Circuits, Power and Computing Technologies, 20-21 Mar. 2013, Nagercoil, India. IEEE, 2013, p.752-755. DOI: https://doi.org/10.1109/ICCPCT.2013.6529041.

- Pelgrom, M. J. M.; Dijkmans, E. C. A 3/5 V compatible I/O buffer. IEEE J. Solid-State Circuits, v.30, n.7, p.823-825, 1995. DOI: https://doi.org/10.1109/4.391124.

- Ker, M.-D.; Tsai, C.-S. Design of 2.5V/5V mixed-voltage CMOS I/O buffer with only thin oxide device and dynamic N-well bias circuit. Proc. of IEEE Int. Symp. on Circuits and Systems, 25-28 May 2003, Bangkok, Thailand. IEEE, 2003, v.4, p.97-100. DOI: https://doi.org/10.1109/ISCAS.2003.1206197.

- Clark, L. T. A high-voltage output buffer fabricated on a 2V CMOS technology. Proc. of Symp. on VLSI Circuits, 17-19 Jun 1999, Kyoto, Japan. IEEE, 1999, p.61-62. DOI: https://doi.org/10.1109/VLSIC.1999.797236.

- Chen, Shih-Lun; Ker, Ming-Dou. An output buffer for 3.3-V applications in a 0.13-µm 1/2.5-V CMOS process. IEEE Trans. Circuits and Systems II: Express Briefs, v.54, n.1, p.14-18, 2007. DOI: https://doi.org/10.1109/TCSII.2006.883202.

- Yu, Chien-Cheng; Wang, Wei-Ping; Liu, Bin-Da. A new level converter for low-power applications. Proc. of IEEE Int. Symp. on Circuits and Systems, 6-9 May 2001, Sydney, Australia. IEEE, 2001, v.1, p.113-116. DOI: https://doi.org/10.1109/ISCAS.2001.921801.

- Otsuka, N.; Horowitz, M. A. Circuit techniques for 1.5-V power supply flash memory. IEEE J. Solid-State Circuits, v.32, n.8, p.1217-1230, 1997. DOI: https://doi.org/10.1109/4.604078.

- Kanno, Y.; Mizuno, H.; Tanaka, K.; Watanabe, T. Level converters with high immunity to power-supply bouncing for high-speed sub-1-V LSIs. Proc. of Symp. on VLSI Circuits, 15-17 Jul. 2000, Honolulu, HI, USA. IEEE, 2000, p.202-203. DOI: https://doi.org/10.1109/VLSIC.2000.852890.

- Wang, W.-T.; Ker, M.-D.; Chiang, M.-C.; Chen, C.-H. Level shifters for high-speed 1 V to 3.3 V interfaces in a 0.13 µm Cu-interconnection/low-k CMOS technology. Proc. of IEEE Int. Symp. on VLSI Technology, Systems and Applications, 18-20 Apr. 2001, Hsinchu, Taiwan. IEEE, 2001, p.307-310. DOI: https://doi.org/10.1109/VTSA.2001.934546.

- Ping-Yuan, Ch.; Chien-Cheng, Yu. A voltage level converter circuit design with low power consumption. Proc. of 6th IEEE Int. Conf. on ASIC, 24-27 Oct. 2005, Shanghai, China. IEEE, 2005, p.358-359. DOI: https://doi.org/10.1109/ICASIC.2005.1611324.

##submission.downloads##

Опубліковано

2017-11-30

Як цитувати

Махендранат, Б., & Сринивасулу, А. (2017). Выходной буфер 1,8 В на основе 180 нм КМОП технологии для устройств 3,3 В. Вісті вищих учбових закладів. Радіоелектроніка, 60(11), 663–672. https://doi.org/10.20535/S0021347017110061

Номер

Розділ

Оригінальні статті