Разработка и сравнительный анализ схем перспективной технологии FinFET

DOI:

https://doi.org/10.20535/S0021347014120048Ключові слова:

технология FinFET, низкая мощность, помехоустойчивость, эффект короткого канала, мощность тока утечкиАнотація

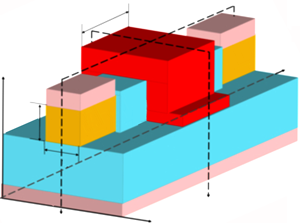

На основе анализа проблем технологии полевых транзисторов MOSFET (Metal Oxide Semiconductor Field Effect Transistor) со структурой металл–окисел–полупроводник на базе технологии двойного или множественного затвора с целью обеспечения адекватного управления затвором была разработана технология FinFET, позволяющая дополнительно уменьшить размеры устройства MOSFET. Применение транзисторов MOSFET с двойным затвором (dual-gate или DG MOSFET) позволяет управлять затвором, а, следовательно, каналом между истоком и стоком более эффективно. Следовательно, многие проявления эффекта короткого канала, такие как под-пороговые колебания, уменьшение дифференциального сопротивления стока в области насыщения или DIBL-эффект (Drain Induced Barier Lowering), ток утечки затвора, пробой и т. д. не возникают с ростом концентрации носителей заряда в канале. Данная работа посвящена анализу особенностей конструкции DG MOSFET, в частности FinFET-структур. Рассмотрены FinFET-структура и 4 варианта ее конструкции: SG, LP, IG и IG/LP. Проведен сравнительный анализ таких параметров, как ток утечки закрытого транзистора, задержка, суммарная потребляемая мощность схемы и шумы для 45 нм технологического процесса с помощью программы Cadence Virtuoso.Посилання

- Jovanović V. FinFET technology for wide-channel devices with ultra-thin silicon body / V. Jovanović, T. Suligoj, P. Biljanović, L. K. Nanver // Information and Communication Technology, Electronics and Microelectronics : 31st Int. Convention MIPRO2008, May 26–30, 2008, Opatija, Croatia. — URL : http://ectm.ewi.tudelft.nl/publications_pdf/document1263.pdf.

- Kumar V. R. Submicron 70nm CMOS Logic Design with FINFETs / V. Raj Kumar, A. Alfred Kirubaraj // Int. J. Eng. Sci. Technol. — 2010. — Vol. 2, No. 9. — P. 4751–4758. — URL : http://www.ijest.info/docs/IJEST10-02-09-154.pdf.

- Gu J. Width quantization aware FinFET circuit design / Jie Gu, John Keane, Sachin Sapatnekar, Chris Kim // Custom Integrated Circuits : IEEE Conf. CICC’06, 10–13 Sept. 2006, San Jose, CA : proc. — IEEE, 2006. — P. 337–340. — DOI : http://dx.doi.org/10.1109/CICC.2006.320916.

- FinFET SRAM with enhanced read/write margins / A. Carlson, Z. Guo, S. Balasubramanian, L. T. Pang, T.-J. King Liu, B. Nikolic / SOI : IEEE Int. Conf., 2–5 Oct. 2006, Niagara Falls, NY : proc. — IEEE, 2006. — P. 105–106. — DOI : http://dx.doi.org/10.1109/SOI.2006.284456.

- Muttreja A. CMOS logic design with independent-gate FinFETs / A. Muttreja, N. Agarwal, N. K. Jha // Computer Design : 25th Int. Conf. ICCD, 7–10 Oct. 2007, Lake Tahoe, CA : proc. — IEEE, 2007. — P. 560–567. — DOI : http://dx.doi.org/10.1109/ICCD.2007.4601953.

- Low leakage bulk silicon substrate based SDOI FINFETs / Jia Lio, Zhijiong Luo, Haizhou Yin, Huilong Zhu, Hefei Wang, Feng Yuan // Solid-State and Integrated Circuit Technology : 10th IEEE Int. Conf. ICSICT, 1–4 Nov. 2010, Shanghai : proc. — IEEE, 2010. — P. 1820–1822. — DOI : http://dx.doi.org/10.1109/ICSICT.2010.5667687.

- Modeling and circuit synthesis for independently controlled double gate FinFET devices / Animesh Datta, Ashish Goel, Riza Tamer Cakici, Hamid Mahmoodi, Dheepa Lekshmanan, Kaushik Roy // IEEE Trans. CAD Integr. Circuits Syst. — Nov. 2007. — Vol. 26, No. 11. — P. 1957–1966. — DOI : http://dx.doi.org/10.1109/TCAD.2007.896320.

- Rostami M. Dual-Vth independent-gate FinFETs for low power logic circuits / Masoud Rostami, Kartik Mohanram // IEEE Trans. CAD Integr. Circuits Syst. — Mar. 2011. — Vol. 30, No. 3. — P. 337–339. — DOI : http://dx.doi.org/10.1109/TCAD.2010.2097310.

- Shanavas I. H. An analogous computation of different techniques for the digital implementation of inverter and NAND logic gates / I. Hameem Shanavas, M. Brindha, V. Nallusamy // Int. J. Inf. Eng. Electronic Business. — Aug. 2012. — Vol. 4, No. 4. — P. 33–38. — URL : http://www.mecs-press.org/ijieeb/ijieeb-v4-n4/v4n4-5.html.

- High-density reduced-stack logic circuit techniques using independent-gate controlled double-gate devices / Meng-Hsueh Chiang, Keunwoo Kim, Ching-Te Chuang, C. Tretz // IEEE Trans. Electron Devices. — Sep. 2006. — Vol. 53, No. 9. — P. 2370–2377. — DOI : http://dx.doi.org/10.1109/TED.2006.881052.

- Design of high-performance digital logic circuits based on FinFET technology / V. Narendar, Wanjul Dattatray R, Sanjeev Rai, R. A. Mishra // Int. J. Computer Applications. — Mar. 2012. — Vol. 41, No. 20. — P. 40–44. — DOI : http://dx.doi.org/10.5120/5812-8104.

- Deepak L. A. Design and implementation of 32nm FINFET based 4x4 SRAM cell array using 1-bit 6T SRAM / Lourts A. Deepak, Likhitha Dhulipalla // Nanoscience, Engineering and Technology : Int. Conf. ICONSET, 28–30 Nov. 2011, Chennai : proc. — IEEE, 2011. — P. 177–180. — DOI : http://dx.doi.org/10.1109/ICONSET.2011.6167948.

- Leakage current: Moore’s law meets static power / N. S. Kim, T. Austin, D. Baauw, T. Mudge, K. Flautner, J. S. Hu, M. J. Irwin, M. Kandemir, V. Narayanan // Computer. — Dec. 2003. — Vol. 36, No. 12. — P. 68–75. — DOI : http://dx.doi.org/10.1109/MC.2003.1250885.

- Tawfik S. A. Low-power and compact sequential circuits with independent-gate FinFETs / Sherif A. Tawfik, Volkan Kursun // IEEE Trans. Electron Devices. — Jan. 2008. — Vol. 55, No. 1. — P. 60–70. — DOI : http://dx.doi.org/10.1109/TED.2007.911039.

- Raj B. Nanoscale FinFET based SRAM cell design: Analysis of performance metric, process variation, underlapped FinFET, and temperature effect / Balwinder Raj, A. K. Saxena, S. Dasgupta // IEEE Circuits and Systems Magazine. — 2011. — Vol. 11, No. 3. — P. 38–50. — DOI : http://dx.doi.org/10.1109/MCAS.2011.942068.

- Retdian N. Voltage controlled ring oscillator with wide tuning range and fast voltage swing / N. Retdian, S. Takagi, N. Fujii // IEEE Asia-Pacific Conf. : ASIC, 2002. — IEEE, 2002. — P. 201–204. — DOI : http://dx.doi.org/10.1109/APASIC.2002.1031567.

- The optimal design of 15 nm gate-length junctionless SOI FinFETs for reducing leakage current / Xi Liu, Meile Wu, Xiaoshi Jin, Rongyan Chuai, Jung-Hee Lee, Jong-Ho Lee // Semicond. Sci. Tech. — 2013. — Vol. 28, No. 10. — P. 105013. — DOI : http://dx.doi.org/10.1088/0268-1242/28/10/105013.

##submission.downloads##

Опубліковано

Як цитувати

Номер

Розділ

Ліцензія

Авторське право (c) 2014 Известия высших учебных заведений. РадиоэлектроникаИздатель журнала Известия высших учебных заведений. Радиоэлектроника (сокр. "Известия вузов. Радиоэлектроника"), Национальный технический университет Украины "Киевский политехнический институт", учитывает, что доступ автора к его статье является важным как для самого автора, так и для спонсоров его исследований. Мы представлены в базе издателей SHERPA/RoMEO как зеленый издатель (green publisher), что позволяет автору выполнять самоархивирование своей статьи. Однако важно, чтобы каждая из сторон четко понимала свои права. Просьба более детально ознакомиться с Политикой самоархивирования нашего журнала.

Политика оплаченного открытого доступа POA (paid open access), принятая в журнале, позволяет автору выполнить все необходимые требования по открытому доступу к своей статье, которые выдвигаются институтом, правительством или фондом при выделении финансирования. Просьба более детально ознакомиться с политикой оплаченного открытого доступа нашего журнала (см. отдельно).

Варианты доступа к статье:

1. Статья в открытом доступе POA (paid open access)

В этом случае права автора определяются лицензией CC BY (Creative Commons Attribution).

2. Статья с последующим доступом по подписке

В этом случае права автора определяются авторским договором, приведенным далее.

- Автор (каждый соавтор) уступает Издателю журнала «Известия высших учебных заведений. Радиоэлектроника» НТУУ «КПИ» на срок действия авторского права эксклюзивные права на материалы статьи, в том числе право на публикацию данной статьи издательством Аллертон Пресс, США (Allerton Press) на английском языке в журнале «Radioelectronics and Communications Systems». Передача авторского права охватывает исключительное право на воспроизведение и распространение статьи, включая оттиски, переводы, фото воспроизведения, микроформы, электронные формы (он- и оффлайн), или любые иные подобные формы воспроизведения, а также право издателя на сублицензирование третьим лицам по своему усмотрению без дополнительных консультаций с автором. При этом журнал придерживается Политики конфиденциальности.

- Передача прав включает право на обработку формы представления материалов с помощью компьютерных программам и систем (баз данных) для их использования и воспроизводства, публикации и распространения в электронном формате и внедрения в системы поиска (базы данных).

- Воспроизведение, размещение, передача или иное распространение или использование материалов, содержащихся в статье должно сопровождаться ссылкой на Журнал и упоминанием Издателя, а именно: название статьи, имя автора (соавторов), название журнала, номер тома, номер выпуска, копирайт авторов и издателя "© Национальный технический университет Украины "Киевский политехнический институт"; © автор(ы)".

- Автор (каждый соавтор) материалов сохраняет все права собственника материалов, включая патентные права на любые процессы, способы или методы и др., а также права на товарные знаки.

- Издатель разрешает автору (каждому соавтору) материалов следующее:

- Право пользоваться печатными или электронными вариантами материалов статьи в форме и содержании, принятыми Издателем для публикации в Журнале. Подробнее см. политики Оплаченного открытого доступа, подписки и самоархивирования.

- Право бесплатно копировать или передавать коллегам копию напечатанной статьи целиком или частично для их личного или профессионального использования, для продвижения академических или научных исследований или для учебного процесса или других информационных целей, не связанных с коммерческими целями.

- Право использовать материалы из опубликованной статьи в написанной автором (соавторами) книге, монографии, учебнике, учебном пособии и других научных и научно-популярных изданиях.

- Право использовать отдельные рисунки или таблицы и отрывки текста из материалов в собственных целях обучения или для включения их в другую работу, которая печатается (в печатном или электронном формате) третьей стороной, или для представления в электронном формате во внутренние компьютерные сети или на внешние сайты автора (соавторов).

- Автор (соавторы) соглашаются, что каждая копия материалов или любая ее часть, распространенная или размещенная ими в печатном или электронном формате, будет содержать указание на авторское право, предусмотренное в Журнале и полную ссылку на Журнал Издателя.

- Автор (соавторы) гарантирует, что материалы являются оригинальной работой и представлены впервые на рассмотрение только в этом Журнале и ранее не публиковались. Если материалы написаны совместно с соавторами, автор гарантирует, что проинформировал их относительно условий публикации материалов и получил их подписи или письменное разрешение подписываться от их имени.

- Если в материалы включаются отрывки из работ или имеются указания на работы, которые охраняются авторским правом и принадлежат третьей стороне, то автору необходимо получить разрешение владельца авторских прав на использование таких материалов в первом случае и сделать ссылку на первоисточник во втором.

- Автор гарантирует, что материалы не содержат клеветнических высказываний и не посягают на права (включая без ограничений авторское право, права на патент или торговую марку) других лиц и не содержат материалы или инструкции, которые могут причинить вред или ущерб третьим лицам. Автор (каждый соавтор) гарантирует, что их публикация не приведет к разглашению секретных или конфиденциальных сведений (включая государственную тайну). Подтверждением этого является Экспертное заключение (см. перечень документов в Правила для авторов).

- Издатель обязуется опубликовать материалы в случае получения статьей положительного решения редколлегии о публикации на основании внешнего рецензирования (см. Политика рецензирования).

- В случае публикации статьи на английском языке в журнале «Radioelectronics and Communications Systems» (Издатель: Аллертон Пресс, США, распространитель Springer) автору (соавторам) выплачивается гонорар после выхода последнего номера журнала года, в котором опубликована данная статья.

- Документ Согласие на публикацию, который подают русскоязычные авторы при подаче статьи в редакцию, является краткой формой данного договора, в котором изложены все ключевые моменты настоящего договора и наличие которого подтверждает согласие автора (соавторов) с ним. Аналогичным документом для англоязычных авторов является Copyright Transfer Agreement (CTA), предоставляемый издательством Allerton Press.

- Настоящий Договор вступает в силу в момент принятия статьи к публикации. Если материалы не принимаются к публикации или до публикации в журнале автор (авторы) отозвал работу, настоящий Договор не приобретает (теряет) силу.